### **Errata Sheet for Stratix V Devices**

ES-01034-1.6 Errata Sheet

This errata sheet provides information about known device issues affecting  $Stratix^{@}V$  production devices.

### **Production Device Issues for Stratix V Devices**

Table 1 lists the issues and the affected Stratix V production devices.

Table 1. Stratix V Production Device Issues (Part 1 of 2)

| Issue                                                                                                                      | Affected Devices                                                             | Planned Fix                                                                              |

|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| "PCIe Gen2 Link Training Error When Using Hard Reset Controller"                                                           | All Stratix V production devices                                             | Software will default to<br>Soft Reset Controller in<br>Quartus II version<br>13.1.      |

| "LVDS Soft-CDR and DPA Modes"                                                                                              | All Stratix V GX/GS/GT production devices                                    | None                                                                                     |

| "Receiver Detect Issue in the PCIe Hard IP"                                                                                | 5SGXA7, 5SGXA5, 5SGXA4,<br>5SGXA3, 5SGSD5, 5SGSD4,<br>5SGSD3, 5SGTC7, 5SGTC5 | 5SGXB5, 5SGXB6,<br>5SGSD6, 5SGSD8,<br>5SGXA9, 5SGXAB,<br>5SGXB9, 5SGXBB,<br>5SEE9, 5SEEB |

| "Partial Reconfiguration (PR) with Compression Not Supported in Configuration via Procotol (CvP) when Encryption Disabled" | All Stratix V production devices                                             | None                                                                                     |

| "False Configuration Failure in Active Serial Multi-Device<br>Configuration x1 Mode"                                       | All Stratix V production devices                                             | None                                                                                     |

| "CMU PLL Range"                                                                                                            | All Stratix V GX and GS production devices                                   | None                                                                                     |

| "Production Device Supply Voltage Requirements"                                                                            | All Stratix V GX and GS production devices                                   | None                                                                                     |

| "ATX PLL Range"                                                                                                            | All Stratix V GX/GS/GT production devices                                    | For faster operation, contact mySupport.                                                 |

| "Unused or Idle Clock Performance Degradation"                                                                             | All Stratix V GX/GS/GT production devices                                    | None                                                                                     |

| "RREF Calibration Resistor Value Changed from $2k\Omega$ to $1.8k\Omega$ "                                                 | All Stratix V GX/GS/GT production devices                                    | None                                                                                     |

101 Innovation Drive San Jose, CA 95134 www.altera.com © 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Table 1. Stratix V Production Device Issues (Part 2 of 2)

| Issue                                                                          | Affected Devices                                                             | Planned Fix                                                                              |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| "M20K Initialization in Partial Reconfiguration"                               | 5SGXA7, 5SGXA5, 5SGXA4,<br>5SGXA3, 5SGSD5, 5SGSD4,<br>5SGSD3, 5SGTC7, 5SGTC5 | 5SGXB5, 5SGXB6,<br>5SGSD6, 5SGSD8,<br>5SGXA9, 5SGXAB,<br>5SGXB9, 5SGXBB,<br>5SEE9, 5SEEB |

| "PCIe Configure Write Operation with Configure Retry Status (CRS) in CvP Mode" | All Stratix V GX/GS/GT production devices                                    | None                                                                                     |

### **PCIe Gen2 Link Training Error When Using Hard Reset Controller**

An intermittent PCIe Gen2 Hard IP link-up issue may occur in Quartus II version 13.0SP1 and earlier.

When using the hard reset controller in a Gen2 native configuration, the Stratix V Hard IP for PCI Express MegaCore function may incorrectly transmit at 5 Gbps instead of the 2.5 Gbps data rate during link training.

#### **Workaround**

For Gen2 configurations that do not use Configuration via Protocol (CvP), follow the instructions in the Knowledge Base Solution for a workaround. For CvP Gen2 configurations, contact mySupport.

#### **LVDS Soft-CDR and DPA Modes**

LVDS receivers in Soft-CDR or DPA mode operating between 650 Mbps to 1.25 Gbps include usage restrictions.

For additional information, contact mySupport.

#### Receiver Detect Issue in the PCIe Hard IP

The Link Training and Status State Machine (LTSSM) in the PCIe Hard IP may become stuck in the Detect. Active state after sending the TXDetectRX pulse. This issue may impact your system only if one of the following PCIe Gen1/Gen2 modes is used:

- Autonomous Hard IP

- Configuration via Protocol using PCIe (CvP) Init mode only

The CvP update mode is not affected. Other PCIe modes are not impacted by this issue. Contact mySupport if you are using an affected device.

# Partial Reconfiguration (PR) with Compression Not Supported in Configuration via Procotol (CvP) when Encryption Disabled

Table 2 shows the PR support with CvP in different combinations of compression and encryption features.

**Table 2. Partial Reconfiguration Support**

| Compression with PR | Encryption with PR | CvP mode | Supported |

|---------------------|--------------------|----------|-----------|

| OFF                 | OFF                | ON       | YES       |

| OFF                 | ON                 | ON       | YES       |

| ON                  | OFF                | ON       | NO        |

| ON                  | ON ON              |          | YES       |

There is no restriction when CvP is **Disabled**. For additional inquiries, contact mySupport.

## False Configuration Failure in Active Serial Multi-Device Configuration x1 Mode

In Active Serial (AS) multi-device configuration x1 mode, you may experience a false configuration error. The failure is indicated by CONF\_DONE going high followed by nSTATUS going low and reconfiguration is initiated repeatedly.

#### **Workaround**

To overcome this issue, perform both of the following:

- 1. Disable the CONF\_DONE error checking in AS multi-device configuration mode:

- a. If you are using Quartus<sup>®</sup> II version 12.0 or older, check the "Disable AS mode CONF\_DONE error check" option. This option can be found in the "Advanced" button under the Convert Programming File window.

- b. If you are using Quartus II version 12.0 SP1 or later, the error checking is disabled automatically for AS multi-device configuration POF file generation.

- 2. Enable the INIT\_DONE pin option:

- a. To ensure successful configuration, Altera recommends you enable the INIT\_DONE optional pin for devices in the configuration chain. On the board, do not tie INIT\_DONE pins together between master and slave devices. Monitor the INIT\_DONE status for each device to ensure successful transition into user-mode.

Other configuration modes (JTAG, Fast Passive Parallel (FPP), Passive Serial (PS) single and multi device configuration, and AS single device configuration) are not affected.

### **CMU PLL Range**

The CMU PLL operating range for a -1 transceiver speed grade has changed and is specified in the *Stratix V Device Datasheet*.

### **Production Device Supply Voltage Requirements**

### C2 and I2 Speed Grade Core Voltage (VCC) Change

The VCC supply voltage for the C2 and I2 speed grades has changed from 0.85 V to 0.9 V. The voltage change is reflected in the Quartus II version 12.0 software, and the *Stratix V Device Datasheet*. The change applies to VCC, VCCHIP and VCCHSSI, which all must be tied to the same regulator when used.

### **Transceiver Voltage Changes**

The *Stratix V Device Handbook* and *Stratix V Devices Family Pin Connection Guidelines* have been updated to reflect the transceiver voltage changes for VCCR\_GXB and VCCT\_GXB.

### Partial Reconfiguration (PR) Power Supply Requirement

For information about speed grade and power supply requirements, contact mySupport.

### **ATX PLL Range**

The ATX PLL range is limited for Stratix V production devices. Table 3 through Table 7 list the specifications for these devices.

You must ensure that the correct ATX PLL location is assigned, based on the data rate desired and the specifications listed in Table 3 through Table 7.

| Table 3. Spec | ifications fo | ır Stratix ' | V GX/GS -1 | Transceiver | PMA Speed Grade |

|---------------|---------------|--------------|------------|-------------|-----------------|

|---------------|---------------|--------------|------------|-------------|-----------------|

| Donno  | Dividere (4)                                 | Top ATX PLL<br>in Transceiver Bank |                  | Bottom Al<br>in Transce        | 11     |       |  |

|--------|----------------------------------------------|------------------------------------|------------------|--------------------------------|--------|-------|--|

| Range  | Dividers (1)                                 | Min Data<br>Rate                   | Max Data<br>Rate | Min Data Max Data<br>Rate Rate |        | Units |  |

| Native | L = 2                                        | 8,000                              | 14,100           | 8,000                          | 13,200 | Mbps  |  |

| /2     | L = 4                                        | 4,000                              | 7,050            | 4,000                          | 6,600  | Mbps  |  |

| /4     | L = 8                                        | 2,000                              | 3,525            | 2,000                          | 3,300  | Mbps  |  |

| /8     | L = 8,<br>Local/Central<br>Clock Divider = 2 | 1,000                              | 1,762.5          | 1,000                          | 1,650  | Mbps  |  |

### Note to Table 3:

- (1) "L" is the post VCO Divider within the ATX PLL. The Local/Central Clock Divider is located within the channel.

- (2) For faster operation, contact mySupport.

To determine the output frequency of the ATX PLL, divide the data rate by 2. For example, an ATX PLL used for a 12.5 Gbps link will have an output frequency of 6.25 GHz. If local clock dividers are used, then the divide factor must be taken into account. For example, an ATX PLL used for 3.125 and 6.25 Gbps data rate links within the same bank would use a common frequency of 3.125 GHz. That clock would directly feed the 6.25 Gbps links as well as feeding a local data divider set to 2 to generate 1.5625 GHz for the 3.125 Gbps link.

Table 4. Specifications for Stratix V GX/GS -2 Transceiver PMA Speed Grade

| Danna  | Dividers (1)                                 | Top ATX PLL<br>in Transceiver Bank |                  | Bottom<br>in Transce | Units  |      |

|--------|----------------------------------------------|------------------------------------|------------------|----------------------|--------|------|

| Range  |                                              | Min Data<br>Rate                   | Max Data<br>Rate | Min Data<br>Rate     |        |      |

| Native | L = 2                                        | 8,000                              | 12,500           | 8,000                | 12,500 | Mbps |

| /2     | L = 4                                        | 4,000                              | 6,600            | 4,000                | 6,600  | Mbps |

| /4     | L = 8                                        | 2,000                              | 3,300            | 2,000                | 3,300  | Mbps |

| /8     | L = 8,<br>Local/Central<br>Clock Divider = 2 | 1,000                              | 1,650            | 1,000                | 1,650  | Mbps |

#### Note to Table 4:

Table 5. Specifications for Stratix V GX/GS -3 Transceiver PMA Speed Grade

| Danna  | Top ATX PLL in Transceiver Bank              |                  | Bottom<br>in Transco | 11               |                  |       |  |

|--------|----------------------------------------------|------------------|----------------------|------------------|------------------|-------|--|

| Range  | , ,                                          | Min Data<br>Rate | Max Data<br>Rate     | Min Data<br>Rate | Max Data<br>Rate | Units |  |

| Native | L = 2                                        | 8,000            | 8,500                | 8,000            | 8,500            | Mbps  |  |

| /2     | L = 4                                        | 4,000            | 6,600                | 4,000            | 5,500            | Mbps  |  |

| /4     | L = 8                                        | 2,000            | 3,300                | 2,000            | 2,750            | Mbps  |  |

| /8     | L = 8,<br>Local/Central<br>Clock Divider = 2 | 1,000            | 1,650                | 1,000            | 1,375            | Mbps  |  |

#### Note to Table 5:

Table 6. Specifications for Stratix V GT -2 Transceiver PMA Speed Grade for GX Channels

| Donne  | Dividers (1)                                 | •                | TX PLL<br>eiver Bank |                  | PLL Left Side<br>ver Bank <i>(2)</i> |                  | PLL Right Side<br>ver Bank <i>(2)</i> | Unito |

|--------|----------------------------------------------|------------------|----------------------|------------------|--------------------------------------|------------------|---------------------------------------|-------|

| Range  |                                              | Min Data<br>Rate | Max Data<br>Rate     | Min Data<br>Rate | Max Data<br>Rate                     | Min Data<br>Rate | Max Data<br>Rate                      | Units |

| Native | L = 2                                        | 8,000            | 12,500               | 8,000            | 12,500                               | 8,000            | 12,500                                | Mbps  |

| /2     | L = 4                                        | 4,000            | 6,600                | 4,000            | 6,600                                | 4,000            | 7,050                                 | Mbps  |

| /4     | L = 8                                        | 2,000            | 3,300                | 2,000            | 3,300                                | 2,000            | 3,525                                 | Mbps  |

| /8     | L = 8,<br>Local/Central<br>Clock Divider = 2 | 1,000            | 1,650                | 1,000            | 1,650                                | 1,000            | 1,762.5                               | Mbps  |

#### Note to Table 6:

- (1) "L" is the post VCO Divider within the ATX PLL. The Local/Central Clock Divider is located within the channel.

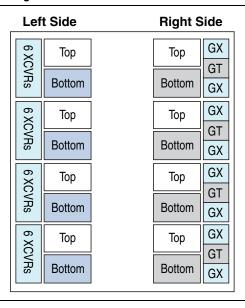

- (2) Refer to Figure 1 for the Left side and Right side positions.

<sup>(1) &</sup>quot;L" is the post VCO Divider within the ATX PLL. The Local/Central Clock Divider is located within the channel.

<sup>(1) &</sup>quot;L" is the post VCO Divider within the ATX PLL. The Local/Central Clock Divider is located within the channel.

| D      | Dividers (1)                                 |                  | Top ATX PLL in Transceiver Bank Bottom ATX PLL Left Side in Transceiver Bank (2) |                  |                  | Bottom ATX F     | 11-:4-           |       |

|--------|----------------------------------------------|------------------|----------------------------------------------------------------------------------|------------------|------------------|------------------|------------------|-------|

| Range  |                                              | Min Data<br>Rate | Max Data<br>Rate                                                                 | Min Data<br>Rate | Max Data<br>Rate | Min Data<br>Rate | Max Data<br>Rate | Units |

| Native | L = 2                                        | 8,000            | 12,500                                                                           | 8,000            | 12,500           | 8,000            | 12,500           | Mbps  |

| /2     | L = 4                                        | 4,000            | 6,600                                                                            | 4,000            | 6,600            | 4,000            | 6,600            | Mbps  |

| /4     | L = 8                                        | 2,000            | 3,300                                                                            | 2,000            | 3,300            | 2,000            | 3,300            | Mbps  |

| /8     | L = 8,<br>Local/Central<br>Clock Divider = 2 | 1,000            | 1,650                                                                            | 1,000            | 1,650            | 1,000            | 1,650            | Mbps  |

Table 7. Specifications for Stratix V GT -3 Transceiver PMA Speed Grade for GX Channels

#### Note to Table 7:

- (1) "L" is the post VCO Divider within the ATX PLL. The Local/Central Clock Divider is located within the channel.

- (2) Refer to Figure 1 for the Left side and Right side positions.

Figure 1. ATX PLL Left and Right Sides

### **Unused or Idle Clock Performance Degradation**

Unused or idle clock dividers of the transceiver can degrade if the devices are powered up to normal operating conditions. This can result in a clock performance degradation of 10% over a period of 5 years. This issue affects designs that will enable unused clock dividers through a new configuration file at a later date. Active clock dividers are not impacted. Non-transceiver circuits are not impacted by this performance degradation.

#### **Guidelines for Eliminating Performance Degradation**

- 1. For unused channels, apply one of the following:

- a. Recompile with Quartus II software, version 12.1 or later to power down the unused clock dividers. This guideline applies to GX channels.

- b. For GX channels designed with Quartus II versions before 12.1, and for GT channels designed with any version of the Quartus II software, instantiate currently unused transceiver channels that may be enabled with a future programming file. This will create activity on currently unused channels. This guideline applies to both GX and GT channels.

- 2. For used (configured) channels, apply the following:

For any version of the Quartus II software, do not assert the PLL and analog reset signals indefinitely. This guideline applies to both GX and GT channels.

### RREF Calibration Resistor Value Changed from $2k\Omega$ to $1.8k\Omega$

The  $R_{REF}$  calibration resistor value specification has changed from  $2k\Omega$  to  $1.8k\Omega$  with a maximum tolerance of +/-1%.

### **M20K Initialization in Partial Reconfiguration**

M20Ks cannot be configured as ROMs or initialized RAMs using partial reconfiguration (PR). Use MLABs as a workaround.

## PCIe Configure Write Operation with Configure Retry Status (CRS) in CvP Mode

After a reset (fundamental or FLR), the core will respond to Configuration (CFG) requests with a CRS until the soft logic is ready for normal operation. In the case of Configuration Writes (CFGWR), the core will respond with a CRS, but it will still execute the register write. Therefore, after a reset, Configuration Reads (CFGRD) must be issued until a non-CRS response is received from the PCIe core before issuing any CFGWR. This issue only affects CvP mode.

Page 8 Document Revision History

## **Document Revision History**

Table 8 lists the revision history for this errata sheet.

**Table 8. Document Revision History**

| Date           | Version | Changes                                                                                                                                                               |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |         | Added the "PCIe Gen2 Link Training Error When Using Hard Reset Controller" section.                                                                                   |

| September 2013 | 1.6     | <ul> <li>Updated the "C2 and I2 Speed Grade Core Voltage (VCC) Change "section.</li> <li>Renamed "-2 Speed Grade" to "C2 and I2 Speed Grade."</li> </ul>              |

|                |         | ■ Updated the "ATX PLL Range"section.                                                                                                                                 |

|                |         | Added the "LVDS Soft-CDR and DPA Modes" section.                                                                                                                      |

|                |         | Added the "Receiver Detect Issue in the PCIe Hard IP" section.                                                                                                        |

|                |         | <ul> <li>Added the "Partial Reconfiguration (PR) with Compression Not Supported in<br/>Configuration via Procotol (CvP) when Encryption Disabled" section.</li> </ul> |

| July 2013      | 1.5     | ■ Updated the "CMU PLL Range"section.                                                                                                                                 |

| July 2013      | 1.5     | <ul><li>Updated the "Production Device Supply Voltage Requirements" section.</li></ul>                                                                                |

|                |         | <ul> <li>Added the "Partial Reconfiguration (PR) Power Supply Requirement" section.</li> </ul>                                                                        |

|                |         | Updated the "Unused or Idle Clock Performance Degradation" section.                                                                                                   |

|                |         | <ul> <li>Updated the "PCIe Configure Write Operation with Configure Retry Status (CRS) in CvP<br/>Mode" section.</li> </ul>                                           |

| September 2012 | 1.4     | Added Note 2 to Table 8 to close FB #53141.                                                                                                                           |

|                |         | <ul> <li>Added the "False Configuration Failure in Active Serial Multi-Device Configuration x1<br/>Mode" section.</li> </ul>                                          |

| July 2012      | 1.3     | Updated Table 1 and Table 8.                                                                                                                                          |

|                |         | Added Table 6 and Table 7.                                                                                                                                            |

|                |         | Added Figure 1.                                                                                                                                                       |

|                |         | <ul> <li>Added the "False Configuration Failure in Active Serial Multi-Device Configuration x1<br/>Mode" section.</li> </ul>                                          |

|                |         | Updated the "CMU PLL Range" section.                                                                                                                                  |

| June 2012      | 1.2     | Updated the "Production Device Supply Voltage Requirements" section.                                                                                                  |

|                |         | <ul><li>Updated the "Transceiver Voltage Changes" section.</li></ul>                                                                                                  |

|                |         | Updated the "ATX PLL Range" section.                                                                                                                                  |

|                |         | Removed CMU PLL at Channel 01 Driving Channel 0 in Non-Bonded Mode section.                                                                                           |

| May 2012       |         | Added the "CMU PLL Range" section.                                                                                                                                    |

|                | 1.1     | Updated the "ATX PLL Range" section.                                                                                                                                  |

|                | 1.1     | Updated the "Transceiver Voltage Changes" section.                                                                                                                    |

|                |         | Added the "RREF Calibration Resistor Value Changed from 2k W to 1.8k W" section.                                                                                      |

| March 2012     | 1.0     | Initial release.                                                                                                                                                      |