## 1. Cyclone IV Device Datasheet

CYIV-53001-1.5

This chapter describes the electrical and switching characteristics for Cyclone® IV devices. Electrical characteristics include operating conditions and power consumption. Switching characteristics include transceiver specifications, core, and periphery performance. This chapter also describes I/O timing, including programmable I/O element (IOE) delay and programmable output buffer delay.

This chapter includes the following sections:

- "Operating Conditions" on page 1–1

- "Power Consumption" on page 1–15

- "Switching Characteristics" on page 1–16

- "I/O Timing" on page 1–38

- "Glossary" on page 1–38

## **Operating Conditions**

When Cyclone IV devices are implemented in a system, they are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of Cyclone IV devices, you must consider the operating requirements described in this chapter.

Cyclone IV devices are offered in commercial, industrial, extended industrial and, automotive grades. Cyclone IV E devices offer –6 (fastest), –7, –8, –8L, and –9L speed grades for commercial devices, –8L speed grades for industrial devices, and –7 speed grade for extended industrial and automotive devices. Cyclone IV GX devices offer –6 (fastest), –7, and –8 speed grades for commercial devices and –7 speed grade for industrial devices.

In this chapter, a prefix associated with the operating temperature range is attached to the speed grades; commercial with a "C" prefix, industrial with an "I" prefix, and automotive with an "A" prefix. Therefore, commercial devices are indicated as C6, C7, C8, C8L, or C9L per respective speed grade. Industrial devices are indicated as I7, I8, or I8L. Automotive devices are indicated as A7.

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

Cyclone IV Device Handbook, Volume 3 November 2011

Cyclone IV E industrial devices I7 are offered with extended operating temperature range.

## **Absolute Maximum Ratings**

Absolute maximum ratings define the maximum operating conditions for Cyclone IV devices. The values are based on experiments conducted with the device and theoretical modeling of breakdown and damage mechanisms. The functional operation of the device is not implied at these conditions. Table 1–1 lists the absolute maximum ratings for Cyclone IV devices.

Conditions beyond those listed in Table 1–1 cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time have adverse effects on the device.

Table 1–1. Absolute Maximum Ratings for Cyclone IV Devices (1) —Preliminary

| Symbol                | Parameter                                                                                                     | Min  | Max   | Unit |

|-----------------------|---------------------------------------------------------------------------------------------------------------|------|-------|------|

| V <sub>CCINT</sub>    | Core voltage, PCI Express® (PCIe®) hard IP block, and transceiver physical coding sublayer (PCS) power supply | -0.5 | 1.8   | V    |

| V <sub>CCA</sub>      | Phase-locked loop (PLL) analog power supply                                                                   | -0.5 | 3.75  | V    |

| V <sub>CCD_PLL</sub>  | PLL digital power supply                                                                                      | -0.5 | 1.8   | V    |

| V <sub>CCIO</sub>     | I/O banks power supply                                                                                        | -0.5 | 3.9   | V    |

| V <sub>CC_CLKIN</sub> | Differential clock input pins power supply                                                                    | -0.5 | 3.9   | V    |

| V <sub>CCH_GXB</sub>  | Transceiver output buffer power supply                                                                        | -0.5 | 2.625 | V    |

| V <sub>CCA_GXB</sub>  | Transceiver physical medium attachment (PMA) and auxiliary power supply                                       | -0.5 | 2.625 | V    |

| V <sub>CCL_GXB</sub>  | Transceiver PMA and auxiliary power supply                                                                    | -0.5 | 1.8   | V    |

| VI                    | DC input voltage                                                                                              | -0.5 | 3.95  | V    |

| I <sub>OUT</sub>      | DC output current, per pin                                                                                    | -25  | 40    | mA   |

| T <sub>STG</sub>      | Storage temperature                                                                                           | -65  | 150   | °C   |

| T <sub>J</sub>        | Operating junction temperature                                                                                | -40  | 125   | °C   |

#### Note to Table 1-1:

## **Maximum Allowed Overshoot or Undershoot Voltage**

During transitions, input signals may overshoot to the voltage shown in Table 1–2 and undershoot to -2.0 V for a magnitude of currents less than 100 mA and for periods shorter than 20 ns. Table 1-2 lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage over the lifetime of the device. The maximum allowed overshoot duration is specified as a percentage of high-time over the lifetime of the device.

<sup>(1)</sup> Supply voltage specifications apply to voltage readings taken at the device pins with respect to ground, not at the power supply.

A DC signal is equivalent to 100% duty cycle. For example, a signal that overshoots to 4.3~V can only be at 4.3~V for 65% over the lifetime of the device; for a device lifetime of 10~V years, this amounts to 65/10ths of a year.

Table 1–2. Maximum Allowed Overshoot During Transitions over a 10-Year Time Frame for Cyclone IV Devices

| Symbol         | Parameter           | Condition (V)         | Overshoot Duration as % of High Time | Unit |

|----------------|---------------------|-----------------------|--------------------------------------|------|

|                |                     | V <sub>I</sub> = 4.20 | 100                                  | %    |

|                |                     | V <sub>I</sub> = 4.25 | 98                                   | %    |

|                |                     | V <sub>I</sub> = 4.30 | 65                                   | %    |

|                |                     | V <sub>I</sub> = 4.35 | 43                                   | %    |

| V <sub>i</sub> | AC Input<br>Voltage | V <sub>I</sub> = 4.40 | 29                                   | %    |

|                | Voltage             | V <sub>I</sub> = 4.45 | 20                                   | %    |

|                |                     | V <sub>I</sub> = 4.50 | 13                                   | %    |

|                |                     | V <sub>I</sub> = 4.55 | 9                                    | %    |

|                |                     | V <sub>I</sub> = 4.60 | 6                                    | %    |

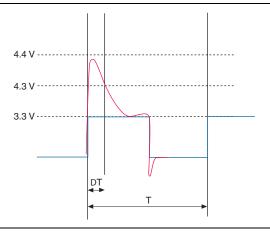

Figure 1–1 shows the methodology to determine the overshoot duration. The overshoot voltage is shown in red and is present on the input pin of the Cyclone IV device at over 4.3 V but below 4.4 V. From Table 1–2, for an overshoot of 4.3 V, the percentage of high time for the overshoot can be as high as 65% over a 10-year period. Percentage of high time is calculated as ([delta T]/T)  $\times$  100. This 10-year period assumes that the device is always turned on with 100% I/O toggle rate and 50% duty cycle signal. For lower I/O toggle rates and situations in which the device is in an idle state, lifetimes are increased.

Figure 1-1. Cyclone IV Devices Overshoot Duration

#### **Operating Conditions**

## **Recommended Operating Conditions**

This section lists the functional operation limits for AC and DC parameters for Cyclone IV devices. Table 1–3 and Table 1–4 list the steady-state voltage and current values expected from Cyclone IV E and Cyclone IV GX devices. All supplies must be strictly monotonic without plateaus.

Table 1–3. Recommended Operating Conditions for Cyclone IV E Devices (1), (2) (Part 1 of 2)

| Symbol                     | Parameter                                             | Conditions                        | Min   | Тур | Max               | Unit |

|----------------------------|-------------------------------------------------------|-----------------------------------|-------|-----|-------------------|------|

| V <sub>CCINT</sub> (3)     | Supply voltage for internal logic,<br>1.2-V operation | _                                 | 1.15  | 1.2 | 1.25              | V    |

| VCCINT (*)                 | Supply voltage for internal logic, 1.0-V operation    | _                                 | 0.97  | 1.0 | 1.03              | V    |

|                            | Supply voltage for output buffers, 3.3-V operation    | _                                 | 3.135 | 3.3 | 3.465             | V    |

|                            | Supply voltage for output buffers, 3.0-V operation    | _                                 | 2.85  | 3   | 3.15              | V    |

| V <sub>CCIO</sub> (3), (4) | Supply voltage for output buffers, 2.5-V operation    | _                                 | 2.375 | 2.5 | 2.625             | V    |

| VCCIO (5)                  | Supply voltage for output buffers, 1.8-V operation    | _                                 | 1.71  | 1.8 | 1.89              | V    |

|                            | Supply voltage for output buffers, 1.5-V operation    | _                                 | 1.425 | 1.5 | 1.575             | V    |

|                            | Supply voltage for output buffers, 1.2-V operation    | _                                 | 1.14  | 1.2 | 1.26              | V    |

| V <sub>CCA</sub> (3)       | Supply (analog) voltage for PLL regulator             | _                                 | 2.375 | 2.5 | 2.625             | V    |

| V (3)                      | Supply (digital) voltage for PLL, 1.2-V operation     | _                                 | 1.15  | 1.2 | 1.25              | V    |

| V <sub>CCD_PLL</sub> (3)   | Supply (digital) voltage for PLL, 1.0-V operation     | _                                 | 0.97  | 1.0 | 1.03              | V    |

| V <sub>I</sub>             | Input voltage                                         | _                                 | -0.5  | _   | 3.6               | V    |

| $V_0$                      | Output voltage                                        | _                                 | 0     | _   | V <sub>CCIO</sub> | V    |

|                            |                                                       | For commercial use                | 0     | _   | 85                | °C   |

| TJ                         | Operating junction temperature                        | For industrial use                | -40   | _   | 100               | °C   |

| IJ                         | Operating junction temperature                        | For extended temperature (5)      | -40   | _   | 125               | °C   |

|                            |                                                       | For automotive use                | -40   |     | 125               | °C   |

| t <sub>RAMP</sub>          | Power supply ramp time                                | Standard power-on reset (POR) (6) | 50 μs | _   | 50 ms             | _    |

|                            |                                                       | Fast POR (7)                      | 50 μs |     | 3 ms              | _    |

Table 1-3. Recommended Operating Conditions for Cyclone IV E Devices (1), (2) (Part 2 of 2)

| Symbol             | Parameter                                                  | Conditions | Min | Тур | Max | Unit |

|--------------------|------------------------------------------------------------|------------|-----|-----|-----|------|

| I <sub>Diode</sub> | Magnitude of DC current across PCI-clamp diode when enable | _          | _   | _   | 10  | mA   |

#### Notes to Table 1-3:

- (1) Cyclone IV E 1.0 V core voltage devices only support C8L, C9L, and I8L speed grades. Cyclone IV E 1.2 V core voltage devices only support C6, C7, C8, I7, and A7 speed grades.

- (2) V<sub>CCIO</sub> for all I/O banks must be powered up during device operation. All VCCA pins must be powered to 2.5 V (even when PLLs are not used) and must be powered up and powered down at the same time.

- (3) V<sub>CC</sub> must rise monotonically.

- (4)  $V_{\text{CCIO}}$  powers all input buffers.

- (5) The I7 devices support extended operating junction temperature up to 125°C (usual range is -40°C to 100°C). When using I7 devices at the extended junction temperature ranging from -40°C to 125°C, select C8 as the target device when designing in the Quartus® II software. The I7 devices meet all C8 timing specifications when I7 devices operate beyond 100°C and up to 125°C.

- (6) The POR time for Standard POR ranges between 50 and 200 ms. Each individual power supply must reach the recommended operating range within 50 ms.

- (7) The POR time for Fast POR ranges between 3 and 9 ms. Each individual power supply must reach the recommended operating range within 3 ms.

Table 1-4. Recommended Operating Conditions for Cyclone IV GX Devices (Part 1 of 2)—Preliminary

| Symbol                     | Parameter                                                          | Conditions  | Min   | Тур | Max   | Unit |

|----------------------------|--------------------------------------------------------------------|-------------|-------|-----|-------|------|

| V <sub>CCINT</sub> (3)     | Core voltage, PCIe hard IP block, and transceiver PCS power supply | _           | 1.16  | 1.2 | 1.24  | V    |

| V <sub>CCA</sub> (1), (3)  | PLL analog power supply                                            | _           | 2.375 | 2.5 | 2.625 | V    |

| V <sub>CCD_PLL</sub> (2)   | PLL digital power supply                                           | <del></del> | 1.16  | 1.2 | 1.24  | V    |

|                            | I/O banks power supply for 3.3-V operation                         | _           | 3.135 | 3.3 | 3.465 | V    |

|                            | I/O banks power supply for 3.0-V operation                         | _           | 2.85  | 3   | 3.15  | V    |

| V <sub>CCIO</sub> (3), (4) | I/O banks power supply for 2.5-V operation                         | _           | 2.375 | 2.5 | 2.625 | V    |

| VCCIO (=7)(17)             | I/O banks power supply for 1.8-V operation                         | _           | 1.71  | 1.8 | 1.89  | V    |

|                            | I/O banks power supply for 1.5-V operation                         | _           | 1.425 | 1.5 | 1.575 | V    |

|                            | I/O banks power supply for 1.2-V operation                         | _           | 1.14  | 1.2 | 1.26  | V    |

|                            | Differential clock input pins power supply for 3.3-V operation     | _           | 3.135 | 3.3 | 3.465 | V    |

|                            | Differential clock input pins power supply for 3.0-V operation     | _           | 2.85  | 3   | 3.15  | V    |

| V <sub>CC_CLKIN</sub>      | Differential clock input pins power supply for 2.5-V operation     | _           | 2.375 | 2.5 | 2.625 | V    |

| (3), (5), (6)              | Differential clock input pins power supply for 1.8-V operation     | _           | 1.71  | 1.8 | 1.89  | V    |

|                            | Differential clock input pins power supply for 1.5-V operation     | _           | 1.425 | 1.5 | 1.575 | V    |

|                            | Differential clock input pins power supply for 1.2-V operation     | _           | 1.14  | 1.2 | 1.26  | V    |

Table 1-4. Recommended Operating Conditions for Cyclone IV GX Devices (Part 2 of 2)—Preliminary

| Symbol               | Parameter                                                   | Conditions                        | Min   | Тур | Max               | Unit |

|----------------------|-------------------------------------------------------------|-----------------------------------|-------|-----|-------------------|------|

| V <sub>CCH_GXB</sub> | Transceiver output buffer power supply                      | _                                 | 2.375 | 2.5 | 2.625             | V    |

| V <sub>CCA_GXB</sub> | Transceiver PMA and auxiliary power supply                  | _                                 | 2.375 | 2.5 | 2.625             | V    |

| V <sub>CCL_GXB</sub> | Transceiver PMA and auxiliary power supply                  | _                                 | 1.16  | 1.2 | 1.24              | V    |

| V <sub>I</sub>       | DC input voltage                                            | _                                 | -0.5  |     | 3.6               | V    |

| V <sub>0</sub>       | DC output voltage                                           | _                                 | 0     | _   | V <sub>CCIO</sub> | V    |

| т                    | Operating junction temperature                              | For commercial use                | 0     |     | 85                | °C   |

| T <sub>J</sub>       | Operating junction temperature                              | For industrial use                | -40   | _   | 100               | °C   |

| t <sub>RAMP</sub>    | Power supply ramp time                                      | Standard power-on reset (POR) (7) | 50 μs | _   | 50 ms             | _    |

|                      |                                                             | Fast POR (8)                      | 50 μs |     | 3 ms              | _    |

| I <sub>Diode</sub>   | Magnitude of DC current across PCI-clamp diode when enabled | _                                 |       |     | 10                | mA   |

#### Notes to Table 1-4:

- (1) All VCCA pins must be powered to 2.5 V (even when PLLs are not used) and must be powered up and powered down at the same time.

- (2) You must connect  $V_{CCD\ PLL}$  to  $V_{CCINT}$  through a decoupling capacitor and ferrite bead.

- (3) Power supplies must rise monotonically.

- (4) V<sub>CCIO</sub> for all I/O banks must be powered up during device operation. Configurations pins are powered up by V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 where I/O Banks 3 and 9 only support V<sub>CCIO</sub> of 1.5, 1.8, 2.5, 3.0, and 3.3 V. For fast passive parallel (FPP) configuration mode, the V<sub>CCIO</sub> level of I/O Bank 8 must be powered up to 1.5, 1.8, 2.5, 3.0, and 3.3 V.

- (5) You must set  $V_{\text{CC\_CLKIN}}$  to 2.5 V if you use CLKIN as a high-speed serial interface (HSSI) refclk or as a DIFFCLK input.

- (6) The CLKIN pins in I/O Banks 3B and 8B can support single-ended I/O standard when the pins are used to clock left PLLs in non-transceiver applications.

- (7) The POR time for Standard POR ranges between 50 and 200 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 50 ms.

- (8) The POR time for Fast POR ranges between 3 and 9 ms. V<sub>CCINT</sub>, V<sub>CCA</sub>, and V<sub>CCIO</sub> of I/O Banks 3, 8, and 9 must reach the recommended operating range within 3 ms.

#### **ESD Performance**

This section lists the electrostatic discharge (ESD) voltages using the human body model (HBM) and charged device model (CDM) for Cyclone IV devices general purpose I/Os (GPIOs) and high-speed serial interface (HSSI) I/Os. Table 1–5 lists the ESD for Cyclone IV devices GPIOs and HSSI I/Os.

Table 1-5. ESD for Cyclone IV Devices GPIOs and HSSI I/Os

| Symbol              | Parameter                             | Passing Voltage | Unit |

|---------------------|---------------------------------------|-----------------|------|

| V                   | ESD voltage using the HBM (GPIOs) (1) | ± 2000          | V    |

| V <sub>ESDHBM</sub> | ESD using the HBM (HSSI I/Os) (2)     | ± 1000          | V    |

| V                   | ESD using the CDM (GPIOs)             | ± 500           | V    |

| V <sub>ESDCDM</sub> | ESD using the CDM (HSSI I/Os) (2)     | ± 250           | V    |

#### Notes to Table 1-5:

- (1) The passing voltage for EP4CGX15 and EP4CGX30 row I/Os is ±1000V.

- (2) This value is applicable only to Cyclone IV GX devices.

### **DC** Characteristics

This section lists the I/O leakage current, pin capacitance, on-chip termination (OCT) tolerance, and bus hold specifications for Cyclone IV devices.

## **Supply Current**

The device supply current requirement is the minimum current drawn from the power supply pins that can be used as a reference for power size planning. Use the Excel-based early power estimator (EPE) to get the supply current estimates for your design because these currents vary greatly with the resources used. Table 1–6 lists the I/O pin leakage current for Cyclone IV devices.

Table 1-6. I/O Pin Leakage Current for Cyclone IV Devices (1), (2)

| Symbol          | Parameter                         | Conditions                                 | Device | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|--------------------------------------------|--------|-----|-----|-----|------|

| I <sub>I</sub>  | Input pin leakage current         | $V_I = 0 V \text{ to } V_{CCIOMAX}$        | _      | -10 | _   | 10  | μА   |

| I <sub>OZ</sub> | Tristated I/O pin leakage current | $V_0 = 0 \text{ V to } V_{\text{CCIOMAX}}$ | _      | -10 | _   | 10  | μА   |

#### Notes to Table 1-6:

- This value is specified for normal device operation. The value varies during device power-up. This applies for all V<sub>CCIO</sub> settings (3.3, 3.0, 2.5, 1.8, 1.5, and 1.2 V).

- (2) The 10  $\mu$ A I/O leakage current limit is applicable when the internal clamping diode is off. A higher current can be observed when the diode is on.

#### **Bus Hold**

The bus hold retains the last valid logic state after the source driving it either enters the high impedance state or is removed. Each I/O pin has an option to enable bus hold in user mode. Bus hold is always disabled in configuration mode.

Table 1–7 lists bus hold specifications for Cyclone IV devices.

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 1 of 2) (1)—Preliminary

|                                            |                                                | V <sub>CCIO</sub> (V) |      |     |      |     |      |     |      |     |      |     |      |      |

|--------------------------------------------|------------------------------------------------|-----------------------|------|-----|------|-----|------|-----|------|-----|------|-----|------|------|

| Parameter                                  | Condition                                      | 1.2                   |      | 1.5 |      | 1.8 |      | 2.5 |      | 3.0 |      | 3.3 |      | Unit |

|                                            |                                                | Min                   | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  | Min | Max  |      |

| Bus hold<br>low,<br>sustaining<br>current  | V <sub>IN</sub> > V <sub>IL</sub> (maximum)    | 8                     | _    | 12  | _    | 30  | _    | 50  | _    | 70  | _    | 70  | _    | μА   |

| Bus hold<br>high,<br>sustaining<br>current | V <sub>IN</sub> < V <sub>IL</sub><br>(minimum) | -8                    | _    | -12 | _    | -30 | _    | -50 | _    | -70 | _    | -70 | _    | μА   |

| Bus hold<br>low,<br>overdrive<br>current   | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _                     | 125  | _   | 175  |     | 200  | _   | 300  | _   | 500  | _   | 500  | μА   |

| Bus hold<br>high,<br>overdrive<br>current  | 0 V < V <sub>IN</sub> < V <sub>CCIO</sub>      | _                     | -125 | _   | -175 | _   | -200 | _   | -300 | _   | -500 | _   | -500 | μА   |

Table 1–7. Bus Hold Parameter for Cyclone IV Devices (Part 2 of 2) (1)—Preliminary

| Parameter           |           |     |     |       |       |      | V <sub>CCIO</sub> | (V) |     |     |     |     |     |      |

|---------------------|-----------|-----|-----|-------|-------|------|-------------------|-----|-----|-----|-----|-----|-----|------|

|                     | Condition | 1.2 |     | 1     | 1.5   |      | 1.8               |     | 2.5 |     | .0  | 3.3 |     | Unit |

|                     |           | Min | Max | Min   | Max   | Min  | Max               | Min | Max | Min | Max | Min | Max |      |

| Bus hold trip point | _         | 0.3 | 0.9 | 0.375 | 1.125 | 0.68 | 1.07              | 0.7 | 1.7 | 0.8 | 2   | 0.8 | 2   | V    |

#### Note to Table 1-7:

(1) Bus hold trip points are based on the calculated input voltages from the JEDEC standard.

## **OCT Specifications**

Table 1–8 lists the variation of OCT without calibration across process, temperature, and voltage (PVT).

Table 1-8. Series OCT Without Calibration Specifications for Cyclone IV Devices—Preliminary

|                                |                       | · Tolerance        |                                                               |      |

|--------------------------------|-----------------------|--------------------|---------------------------------------------------------------|------|

| Description                    | V <sub>CCIO</sub> (V) | Commercial Maximum | Industrial, Extended<br>industrial, and<br>Automotive Maximum | Unit |

|                                | 3.0                   | ±30                | ±40                                                           | %    |

| Ocales OOT willbrook           | 2.5                   | ±30                | ±40                                                           | %    |

| Series OCT without calibration | 1.8                   | ±40                | ±50                                                           | %    |

| danstation                     | 1.5                   | ±50                | ±50                                                           | %    |

|                                | 1.2                   | ±50                | ±50                                                           | %    |

OCT calibration is automatically performed at device power-up for OCT-enabled I/Os.

Table 1–9 lists the OCT calibration accuracy at device power-up.

Table 1–9. Series OCT with Calibration at Device Power-Up Specifications for Cyclone IV Devices —Preliminary

|                       |                       | Calibration        | n Accuracy                                                    |      |

|-----------------------|-----------------------|--------------------|---------------------------------------------------------------|------|

| Description           | V <sub>CCIO</sub> (V) | Commercial Maximum | Industrial, Extended<br>industrial, and<br>Automotive Maximum | Unit |

|                       | 3.0                   | ±10                | ±10                                                           | %    |

| Series OCT with       | 2.5                   | ±10                | ±10                                                           | %    |

| calibration at device | 1.8                   | ±10                | ±10                                                           | %    |

| power-up              | 1.5                   | ±10                | ±10                                                           | %    |

|                       | 1.2                   | ±10                | ±10                                                           | %    |

The OCT resistance may vary with the variation of temperature and voltage after calibration at device power-up. Use Table 1–10 and Equation 1–1 to determine the final OCT resistance considering the variations after calibration at device power-up. Table 1–10 lists the change percentage of the OCT resistance with voltage and temperature.

Table 1–10. OCT Variation After Calibration at Device Power-Up for Cyclone IV Devices— Preliminary

| Nominal Voltage | dR/dT (%/°C) | dR/dV (%/mV) |

|-----------------|--------------|--------------|

| 3.0             | 0.262        | -0.026       |

| 2.5             | 0.234        | -0.039       |

| 1.8             | 0.219        | -0.086       |

| 1.5             | 0.199        | -0.136       |

| 1.2             | 0.161        | -0.288       |

## Equation 1-1. Final OCT Resistance (1), (2), (3), (4), (5), (6)

#### Notes to Equation 1-1:

- (1) T<sub>2</sub> is the final temperature.

- (2) T<sub>1</sub> is the initial temperature.

- (3) MF is multiplication factor.

- (4) R<sub>final</sub> is final resistance.

- (5) R<sub>initial</sub> is initial resistance.

- (6) Subscript  $_{x}$  refers to both  $_{V}$  and  $_{T}$ .

- (7)  $\Delta R_V$  is a variation of resistance with voltage.

- (8)  $\Delta R_T$  is a variation of resistance with temperature.

- (9) dR/dT is the change percentage of resistance with temperature after calibration at device power-up.

- (10) dR/dV is the change percentage of resistance with voltage after calibration at device power-up.

- (11) V<sub>2</sub> is final voltage.

- (12)  $V_1$  is the initial voltage.

Example 1–1 shows how to calculate the change of 50- $\Omega$  I/O impedance from 25°C at 3.0 V to 85°C at 3.15 V.

### Example 1-1. Impedance Change

$$\Delta R_V = (3.15 - 3) \times 1000 \times -0.026 = -3.83$$

$$\Delta R_T = (85 - 25) \times 0.262 = 15.72$$

Because  $\Delta R_V$  is negative,

$$MF_V = 1 / (3.83/100 + 1) = 0.963$$

Because  $\Delta R_T$  is positive,

$$MF_T = 15.72/100 + 1 = 1.157$$

$$MF = 0.963 \times 1.157 = 1.114$$

$$R_{final} = 50 \times 1.114 = 55.71 \Omega$$

## Pin Capacitance

Table 1–11 lists the pin capacitance for Cyclone IV devices.

Table 1–11. Pin Capacitance for Cyclone IV Devices —Preliminary

| Symbol              | Parameter                                                                                                | Typical –<br>Quad Flat<br>Pack<br>(QFP) | Typical –<br>Quad Flat<br>No Leads<br>(QFN) | Typical –<br>Fineline<br>BGA<br>(FBGA) | Unit |

|---------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------|----------------------------------------|------|

| $C_{IOTB}$          | Input capacitance on top and bottom I/O pins                                                             | 7                                       | 7                                           | 6                                      | pF   |

| C <sub>IOLR</sub>   | Input capacitance on right I/O pins                                                                      | 7                                       | 7                                           | 5                                      | pF   |

| C <sub>LVDSLR</sub> | Input capacitance on right I/O pins with dedicated LVDS output                                           | 8                                       | 8                                           | 7                                      | pF   |

| C <sub>VREFLR</sub> | Input capacitance on right dual-purpose $\ensuremath{VREF}$ pin when used as $V_{REF}$ or user I/O pin   | 21                                      | 21                                          | 21                                     | pF   |

| C <sub>VREFTB</sub> | Input capacitance on top and bottom dual-purpose ${\tt VREF}$ pin when used as $V_{REF}$ or user I/O pin | 23 (2)                                  | 23                                          | 23                                     | pF   |

| C <sub>CLKTB</sub>  | Input capacitance on top and bottom dedicated clock input pins                                           | 7                                       | 7                                           | 6                                      | pF   |

| C <sub>CLKLR</sub>  | Input capacitance on right dedicated clock input pins                                                    | 6                                       | 6                                           | 5                                      | pF   |

#### Notes to Table 1-11:

- (1) When you use the VREF pin as a regular input or output, you can expect a reduced performance of toggle rate and t<sub>CO</sub> because of higher pin capacitance.

- (2)  $C_{VREFTB}$  for the EP4CE22 device is 30 pF.

### Internal Weak Pull-Up and Weak Pull-Down Resistor

Table 1-12 lists the weak pull-up and pull-down resistor values for Cyclone IV devices.

Table 1–12. Internal Weak Pull-Up and Weak Pull-Down Resistor Values for Cyclone IV Devices (1) —Preliminary

| Symbol           | Parameter                                                                | Conditions                                            | Min          | Тур | Max | Unit |  |

|------------------|--------------------------------------------------------------------------|-------------------------------------------------------|--------------|-----|-----|------|--|

|                  |                                                                          | $V_{CCIO} = 3.3 \text{ V} \pm 5\% \ ^{(2)}, \ ^{(3)}$ |              |     |     |      |  |

|                  | Value of the I/O pin pull-up resistor                                    | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (2), (3)           | 7 28<br>8 35 | 28  | 47  | kΩ   |  |

| D                | before and during configuration, as                                      | $V_{CCIO} = 2.5 \text{ V} \pm 5\%$ (2), (3)           | 8            | 35  | 61  | kΩ   |  |

| R_ <sub>PU</sub> | well as user mode if you enable the programmable pull-up resistor option | $V_{CCIO} = 1.8 \text{ V} \pm 5\%$ (2), (3)           | 10           | 57  | 108 | kΩ   |  |

|                  |                                                                          | $V_{CCIO} = 1.5 \text{ V} \pm 5\%$ (2), (3)           | 13           | 82  | 163 | kΩ   |  |

|                  |                                                                          | $V_{CCIO} = 1.2 \text{ V} \pm 5\%$ (2), (3)           | 19           | 143 | 351 | kΩ   |  |

|                  |                                                                          | $V_{CCIO} = 3.3 \text{ V} \pm 5\%$ (4)                | 6            | 19  | 30  | kΩ   |  |

|                  | Value of the I/O min and down resistant                                  | $V_{CCIO} = 3.0 \text{ V} \pm 5\%$ (4)                | 6            | 22  | 36  | kΩ   |  |

| R_PD             | Value of the I/O pin pull-down resistor before and during configuration  | $V_{CCIO} = 2.5 \text{ V} \pm 5\%$ (4)                | 6            | 25  | 43  | kΩ   |  |

|                  | bototo and daring configuration                                          | V <sub>CCIO</sub> = 1.8 V ± 5% (4)                    | 7            | 35  | 71  | kΩ   |  |

|                  |                                                                          | $V_{CCIO} = 1.5 \text{ V} \pm 5\%$ (4)                | 8            | 50  | 112 | kΩ   |  |

#### Notes to Table 1-12:

- (1) All I/O pins have an option to enable weak pull-up except the configuration, test, and JTAG pins. The weak pull-down feature is only available for JTAG TCK.

- (2) Pin pull-up resistance values may be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (3)  $R_{PU} = (V_{CC10} V_1)/I_{R_PU}$ Minimum condition:  $-40^{\circ}C$ ;  $V_{CC10} = V_{CC} + 5\%$ ,  $V_1 = V_{CC} + 5\% 50$  mV; Typical condition:  $25^{\circ}C$ ;  $V_{CC10} = V_{CC}$ ,  $V_1 = 0$  V;  $V_2 = 0$  V;  $V_3 = 0$  V;  $V_4 = 0$  V and  $V_5 = 0$  V and  $V_6 = 0$  V and  $V_7 = 0$  V and  $V_8 = 0$  V and  $V_$

- Maximum condition:  $100^{\circ}\text{C}$ ;  $V_{\text{CCIO}} = V_{\text{CC}} 5\%$ ,  $V_{\text{I}} = 0$  V; in which  $V_{\text{I}}$  refers to the input voltage at the I/O pin.

- (4)  $R_{PD} = V_I/I_{RPD}$

- Minimum condition: -40°C;  $V_{CCIO} = V_{CC} + 5\%$ ,  $V_I = 50$  mV;

- Typical condition: 25°C;  $V_{CCIO} = V_{CC}$ ,  $V_1 = V_{CC} 5\%$ ; Maximum condition: 100°C;  $V_{CCIO} = V_{CC} 5\%$ ,  $V_1 = V_{CC} 5\%$ ; in which  $V_1$  refers to the input voltage at the I/O pin.

### **Hot-Socketing**

Table 1–13 lists the hot-socketing specifications for Cyclone IV devices.

Table 1–13. Hot-Socketing Specifications for Cyclone IV Devices —Preliminary

| Symbol                  | Parameter                         | Maximum  |

|-------------------------|-----------------------------------|----------|

| I <sub>IOPIN(DC)</sub>  | DC current per I/O pin            | 300 μΑ   |

| I <sub>IOPIN(AC)</sub>  | AC current per I/O pin            | 8 mA (1) |

| I <sub>XCVRTX(DC)</sub> | DC current per transceiver TX pin | 100 mA   |

| I <sub>XCVRRX(DC)</sub> | DC current per transceiver RX pin | 50 mA    |

#### Note to Table 1-13:

(1) The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns, |IIOPIN| = C dv/dt, in which C is the I/O pin capacitance and dv/dt is the slew rate.

During hot-socketing, the I/O pin capacitance is less than 15 pF and the clock pin capacitance is less than 20 pF.

### **Schmitt Trigger Input**

Cyclone IV devices support Schmitt trigger input on the TDI, TMS, TCK, nSTATUS, nCONFIG, nCE, CONF\_DONE, and DCLK pins. A Schmitt trigger feature introduces hysteresis to the input signal for improved noise immunity, especially for signals with slow edge rate. Table 1-14 lists the hysteresis specifications across the supported  $V_{\rm CCIO}$  range for Schmitt trigger inputs in Cyclone IV devices.

Table 1–14. Hysteresis Specifications for Schmitt Trigger Input in Cyclone IV Devices—Preliminary

| Symbol               | Parameter                      | Conditions (V)          | Minimum | Unit |

|----------------------|--------------------------------|-------------------------|---------|------|

|                      |                                | $V_{CCIO} = 3.3$        | 200     | mV   |

| V                    | Hysteresis for Schmitt trigger | V <sub>CCIO</sub> = 2.5 | 200     | mV   |

| V <sub>SCHMITT</sub> | input                          | V <sub>CCIO</sub> = 1.8 | 140     | mV   |

|                      |                                | V <sub>CCIO</sub> = 1.5 | 110     | mV   |

## I/O Standard Specifications

The following tables list input voltage sensitivities ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ), for various I/O standards supported by Cyclone IV devices. Table 1–15 through Table 1–20 provide the I/O standard specifications for Cyclone IV devices.

Table 1–15. Single-Ended I/O Standard Specifications for Cyclone IV Devices (1). (2) —Preliminary

| •                    | _     |                      | -     |      | -                           | _                           |                         | _                           |                             |                 |                 |

|----------------------|-------|----------------------|-------|------|-----------------------------|-----------------------------|-------------------------|-----------------------------|-----------------------------|-----------------|-----------------|

| I/O Standard         |       | V <sub>CCIO</sub> (V | )     | V    | <sub>L</sub> (V)            | V                           | / <sub>IH</sub> (V)     | V <sub>OL</sub> (V)         | V <sub>OH</sub> (V)         | I <sub>OL</sub> | I <sub>OH</sub> |

| I/O Standard         | Min   | Тур                  | Max   | Min  | Max                         | Min                         | Max                     | Max                         | Min                         | (mA)            | (mA)            |

| 3.3-V LVTTL (3)      | 3.135 | 3.3                  | 3.465 | _    | 0.8                         | 1.7                         | 3.6                     | 0.45                        | 2.4                         | 4               | -4              |

| 3.3-V LVCMOS (3)     | 3.135 | 3.3                  | 3.465 | _    | 0.8                         | 1.7                         | 3.6                     | 0.2                         | V <sub>CCIO</sub> - 0.2     | 2               | -2              |

| 3.0-V LVTTL (3)      | 2.85  | 3.0                  | 3.15  | -0.3 | 0.8                         | 1.7                         | V <sub>CCIO</sub> + 0.3 | 0.45                        | 2.4                         | 4               | -4              |

| 3.0-V LVCMOS (3)     | 2.85  | 3.0                  | 3.15  | -0.3 | 0.8                         | 1.7                         | $V_{CCIO} + 0.3$        | 0.2                         | V <sub>CCIO</sub> - 0.2     | 0.1             | -0.1            |

| 2.5 V <sup>(3)</sup> | 2.375 | 2.5                  | 2.625 | -0.3 | 0.7                         | 1.7                         | V <sub>CCIO</sub> + 0.3 | 0.4                         | 2.0                         | 1               | -1              |

| 1.8 V                | 1.71  | 1.8                  | 1.89  | -0.3 | 0.35 x<br>V <sub>CCIO</sub> | 0.65 x<br>V <sub>CCIO</sub> | 2.25                    | 0.45                        | V <sub>CCIO</sub> – 0.45    | 2               | -2              |

| 1.5 V                | 1.425 | 1.5                  | 1.575 | -0.3 | 0.35 x<br>V <sub>CCIO</sub> | 0.65 x<br>V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.25 x<br>V <sub>CCIO</sub> | 0.75 x<br>V <sub>CCIO</sub> | 2               | -2              |

| 1.2 V                | 1.14  | 1.2                  | 1.26  | -0.3 | 0.35 x<br>V <sub>CCIO</sub> | 0.65 x<br>V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.25 x<br>V <sub>CCIO</sub> | 0.75 x<br>V <sub>CCIO</sub> | 2               | -2              |

| 3.0-V PCI            | 2.85  | 3.0                  | 3.15  | _    | 0.3 x<br>V <sub>CCIO</sub>  | 0.5 x<br>V <sub>CCIO</sub>  | V <sub>CCIO</sub> + 0.3 | 0.1 x V <sub>CCIO</sub>     | 0.9 x V <sub>CCIO</sub>     | 1.5             | -0.5            |

| 3.0-V PCI-X          | 2.85  | 3.0                  | 3.15  | _    | 0.35 x<br>V <sub>CCIO</sub> | 0.5 x<br>V <sub>CCIO</sub>  | V <sub>CCIO</sub> + 0.3 | 0.1 x V <sub>CCIO</sub>     | 0.9 x V <sub>CCIO</sub>     | 1.5             | -0.5            |

#### Notes to Table 1-15:

<sup>(1)</sup> For voltage-referenced receiver input waveform and explanation of terms used in Table 1-15, refer to "Glossary" on page 1-38.

<sup>(2)</sup> AC load CL = 10 pF

<sup>(3)</sup> For more information about interfacing Cyclone IV devices with 3.3/3.0/2.5-V LVTTL/LVCMOS I/O standards, refer to AN 447: Interfacing Cyclone III and Cyclone IV Devices with 3.3/3.0/2.5-V LVTTL/LVCMOS I/O Systems.

Table 1–16. Single-Ended SSTL and HSTL I/O Reference Voltage Specifications for Cyclone IV Devices  $^{(1)}$  —Preliminary

| I/O                    |       |     |       |                                                              | V <sub>REF</sub> (V)                                       |                                                              |                            | V <sub>TT</sub> (V) <sup>(2)</sup> |                         |

|------------------------|-------|-----|-------|--------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------|----------------------------|------------------------------------|-------------------------|

| Standard               | Min   | Тур | Max   | Min                                                          | Тур                                                        | Мах                                                          | Min                        | Тур                                | Max                     |

| SSTL-2<br>Class I, II  | 2.375 | 2.5 | 2.625 | 1.19                                                         | 1.25                                                       | 1.31                                                         | V <sub>REF</sub> –<br>0.04 | $V_{REF}$                          | V <sub>REF</sub> + 0.04 |

| SSTL-18<br>Class I, II | 1.7   | 1.8 | 1.9   | 0.833                                                        | 0.9                                                        | 0.969                                                        | V <sub>REF</sub> –<br>0.04 | V <sub>REF</sub>                   | V <sub>REF</sub> + 0.04 |

| HSTL-18<br>Class I, II | 1.71  | 1.8 | 1.89  | 0.85                                                         | 0.9                                                        | 0.95                                                         | 0.85                       | 0.9                                | 0.95                    |

| HSTL-15<br>Class I, II | 1.425 | 1.5 | 1.575 | 0.71                                                         | 0.75                                                       | 0.79                                                         | 0.71                       | 0.75                               | 0.79                    |

| HSTL-12<br>Class I, II | 1.14  | 1.2 | 1.26  | 0.48 x V <sub>CCIO</sub> (3)<br>0.47 x V <sub>CCIO</sub> (4) | 0.5 x V <sub>CCIO</sub> (3)<br>0.5 x V <sub>CCIO</sub> (4) | 0.52 x V <sub>CCIO</sub> (3)<br>0.53 x V <sub>CCIO</sub> (4) | _                          | 0.5 x<br>V <sub>CCIO</sub>         | _                       |

#### Notes to Table 1-16:

- (1) For an explanation of terms used in Table 1–16, refer to "Glossary" on page 1–38.

- (2)  $V_{TT}$  of the transmitting device must track  $V_{REF}$  of the receiving device.

- (3) Value shown refers to DC input reference voltage,  $V_{REF(DC)}$ .

- (4) Value shown refers to AC input reference voltage,  $V_{REF(AC)}$ .

Table 1-17. Single-Ended SSTL and HSTL I/O Standards Signal Specifications for Cyclone IV Devices—Preliminary

| I/O                 | V <sub>IL(</sub> | <sub>DC)</sub> (V)         | VIH                      | <sub>I(DC)</sub> (V)     | V <sub>IL(</sub> | <sub>AC)</sub> (V)         | V <sub>IH</sub>         | <sub>(AC)</sub> (V)      | V <sub>OL</sub> (V)         | V <sub>OH</sub> (V)         | I <sub>OL</sub> | I <sub>OH</sub> |

|---------------------|------------------|----------------------------|--------------------------|--------------------------|------------------|----------------------------|-------------------------|--------------------------|-----------------------------|-----------------------------|-----------------|-----------------|

| Standard            | Min              | Max                        | Min                      | Max                      | Min              | Max                        | Min                     | Max                      | Max                         | Min                         | (mĀ)            | (mÅ)            |

| SSTL-2<br>Class I   | _                | V <sub>REF</sub> –<br>0.18 | V <sub>REF</sub> + 0.18  | _                        | _                | V <sub>REF</sub> – 0.35    | V <sub>REF</sub> + 0.35 | _                        | V <sub>π</sub> –<br>0.57    | V <sub>TT</sub> + 0.57      | 8.1             | -8.1            |

| SSTL-2<br>Class II  |                  | V <sub>REF</sub> – 0.18    | V <sub>REF</sub> + 0.18  | _                        |                  | V <sub>REF</sub> – 0.35    | V <sub>REF</sub> + 0.35 | _                        | V <sub>ττ</sub> – 0.76      | V <sub>TT</sub> + 0.76      | 16.4            | -16.4           |

| SSTL-18<br>Class I  |                  | V <sub>REF</sub> – 0.125   | V <sub>REF</sub> + 0.125 | _                        |                  | V <sub>REF</sub> – 0.25    | V <sub>REF</sub> + 0.25 | _                        | V <sub>ττ</sub> –<br>0.475  | V <sub>TT</sub> + 0.475     | 6.7             | -6.7            |

| SSTL-18<br>Class II | _                | V <sub>REF</sub> – 0.125   | V <sub>REF</sub> + 0.125 | _                        | _                | V <sub>REF</sub> – 0.25    | V <sub>REF</sub> + 0.25 | _                        | 0.28                        | V <sub>CCIO</sub> - 0.28    | 13.4            | -13.4           |

| HSTL-18<br>Class I  | _                | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1   | _                        | _                | V <sub>REF</sub> – 0.2     | V <sub>REF</sub> + 0.2  | _                        | 0.4                         | V <sub>CCIO</sub> – 0.4     | 8               | -8              |

| HSTL-18<br>Class II |                  | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1   | _                        |                  | V <sub>REF</sub> – 0.2     | V <sub>REF</sub> + 0.2  | _                        | 0.4                         | V <sub>CCIO</sub> - 0.4     | 16              | -16             |

| HSTL-15<br>Class I  |                  | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1   | _                        |                  | V <sub>REF</sub> – 0.2     | V <sub>REF</sub> + 0.2  | _                        | 0.4                         | V <sub>CCIO</sub> - 0.4     | 8               | -8              |

| HSTL-15<br>Class II |                  | V <sub>REF</sub> – 0.1     | V <sub>REF</sub> + 0.1   | _                        |                  | V <sub>REF</sub> – 0.2     | V <sub>REF</sub> + 0.2  | _                        | 0.4                         | V <sub>CCIO</sub> - 0.4     | 16              | -16             |

| HSTL-12<br>Class I  | -0.15            | V <sub>REF</sub> – 0.08    | V <sub>REF</sub> + 0.08  | V <sub>CCIO</sub> + 0.15 | -0.24            | V <sub>REF</sub> – 0.15    | V <sub>REF</sub> + 0.15 | V <sub>CCIO</sub> + 0.24 | 0.25 ×<br>V <sub>CCIO</sub> | 0.75 ×<br>V <sub>CCIO</sub> | 8               | -8              |

| HSTL-12<br>Class II | -0.15            | V <sub>REF</sub> – 0.08    | V <sub>REF</sub> + 0.08  | V <sub>CCIO</sub> + 0.15 | -0.24            | V <sub>REF</sub> –<br>0.15 | V <sub>REF</sub> + 0.15 | V <sub>CCIO</sub> + 0.24 | 0.25 ×<br>V <sub>CCIO</sub> | 0.75 ×<br>V <sub>CCIO</sub> | 14              | -14             |

For more information about receiver input and transmitter output waveforms, and for other differential I/O standards, refer to the I/O Features in Cyclone IV Devices chapter.

Table 1–18. Differential SSTL I/O Standard Specifications for Cyclone IV Devices (1)—Preliminary

| I/O Standard           | /O Standard |     | V <sub>Swing</sub> | <sub>I(DC)</sub> (V) | V <sub>X(AC)</sub> (V) |                              |     | V <sub>Swing(AC)</sub> (V)      |     | V <sub>OX(AC)</sub> (V) |                                 |     |                                 |

|------------------------|-------------|-----|--------------------|----------------------|------------------------|------------------------------|-----|---------------------------------|-----|-------------------------|---------------------------------|-----|---------------------------------|

|                        | Min         | Тур | Max                | Min                  | Max                    | Min                          | Тур | Max                             | Min | Max                     | Min                             | Тур | Max                             |

| SSTL-2<br>Class I, II  | 2.375       | 2.5 | 2.625              | 0.36                 | V <sub>CCIO</sub>      | V <sub>CCIO</sub> /2 - 0.2   | _   | V <sub>CCIO</sub> /2<br>+ 0.2   | 0.7 | V <sub>CCI</sub>        | V <sub>CCIO</sub> /2 -<br>0.125 | _   | V <sub>CCIO</sub> /2<br>+ 0.125 |

| SSTL-18<br>Class I, II | 1.7         | 1.8 | 1.90               | 0.25                 | V <sub>CCIO</sub>      | V <sub>CCIO</sub> /2 - 0.175 | _   | V <sub>CCIO</sub> /2<br>+ 0.175 | 0.5 | V <sub>CCI</sub>        | V <sub>CCIO</sub> /2 - 0.125    | _   | V <sub>CCIO</sub> /2<br>+ 0.125 |

Note to Table 1-18:

Table 1–19. Differential HSTL I/O Standard Specifications for Cyclone IV Devices (1)—Preliminary

|                        | V     | V <sub>CCIO</sub> (V) |       |      | <sub>DC)</sub> (V) | V <sub>x</sub>           | V <sub>X(AC)</sub> (V) |                             |                             | V <sub>CM(DC)</sub> (V) |                             |         | V <sub>DIF(AC)</sub> (V)    |  |

|------------------------|-------|-----------------------|-------|------|--------------------|--------------------------|------------------------|-----------------------------|-----------------------------|-------------------------|-----------------------------|---------|-----------------------------|--|

| I/O Standard           | Min   | Тур                   | Max   | Min  | Max                | Min                      | Тур                    | Max                         | Min                         | Тур                     | Max                         | Mi<br>n | Max                         |  |

| HSTL-18<br>Class I, II | 1.71  | 1.8                   | 1.89  | 0.2  | _                  | 0.85                     |                        | 0.95                        | 0.85                        | _                       | 0.95                        | 0.4     | _                           |  |

| HSTL-15<br>Class I, II | 1.425 | 1.5                   | 1.575 | 0.2  | _                  | 0.71                     |                        | 0.79                        | 0.71                        | _                       | 0.79                        | 0.4     | _                           |  |

| HSTL-12<br>Class I, II | 1.14  | 1.2                   | 1.26  | 0.16 | V <sub>CCIO</sub>  | 0.48 x V <sub>CCIO</sub> |                        | 0.52 x<br>V <sub>CCIO</sub> | 0.48 x<br>V <sub>CCIO</sub> |                         | 0.52 x<br>V <sub>CCIO</sub> | 0.3     | 0.48 x<br>V <sub>CCIO</sub> |  |

Note to Table 1-19:

Table 1–20. Differential I/O Standard Specifications for Cyclone IV Devices (1) (Part 1 of 2)—Preliminary

| I/O Standard                   |                                       | V <sub>CCIO</sub> (V) | )     | V <sub>ID</sub> | (mV) | V <sub>IcM</sub> (V) (2) |                                                                                                   |      | Vo  | <sub>D</sub> (mV) | (3) | V <sub>0S</sub> (V) <sup>(3)</sup> |      |       |

|--------------------------------|---------------------------------------|-----------------------|-------|-----------------|------|--------------------------|---------------------------------------------------------------------------------------------------|------|-----|-------------------|-----|------------------------------------|------|-------|

| I/O Stanuaru                   | Min Typ Max Min Max Min Condition Max |                       | Max   | Min             | Тур  | Max                      | Min                                                                                               | Тур  | Max |                   |     |                                    |      |       |

| LVDEOL                         |                                       |                       |       |                 |      | 0.05                     | $D_{MAX} \leq 500 \; Mbps$                                                                        | 1.80 |     |                   |     |                                    |      |       |

| LVPECL<br>(Row I/Os)           | 2.375                                 | 2.5                   | 2.625 | 100             | _    | 0.55                     | $\begin{array}{l} 500 \; \text{Mbps} \leq  D_{\text{MAX}} \\ \leq 700 \; \text{Mbps} \end{array}$ | 1.80 | _   | _                 | _   | _                                  | _    | _     |

|                                |                                       |                       |       |                 |      | 1.05                     | D <sub>MAX</sub> > 700 Mbps                                                                       | 1.55 |     |                   |     |                                    |      |       |

| IV/DEQL                        |                                       |                       |       |                 |      | 0.05                     | $D_{MAX} \leq 500 \text{ Mbps}$                                                                   | 1.80 |     |                   |     |                                    |      |       |

| LVPECL<br>(Column<br>I/Os) (6) | 2.375                                 | 2.5                   | 2.625 | 100             | _    | 0.55                     | $\begin{array}{l} 500 \; \text{Mbps} \leq D_{\text{MAX}} \\ \leq 700 \; \text{Mbps} \end{array}$  | 1.80 | _   | _                 | _   | _                                  | _    | _     |

| 1,00)                          |                                       |                       |       |                 |      | 1.05                     | D <sub>MAX</sub> > 700 Mbps                                                                       | 1.55 |     |                   |     |                                    |      |       |

|                                |                                       |                       |       |                 |      | 0.05                     | $D_{MAX} \leq 500 \; Mbps$                                                                        | 1.80 |     |                   |     |                                    |      |       |

| LVDS (Row<br>I/Os)             | 2.375                                 | 2.5                   | 2.625 | 100             | _    | 0.55                     | $\begin{array}{l} 500 \; Mbps \leq D_{MAX} \\ \leq \; 700 \; Mbps \end{array}$                    | 1.80 | 247 | _                 | 600 | 1.125                              | 1.25 | 1.375 |

|                                |                                       |                       |       |                 |      | 1.05                     | D <sub>MAX</sub> > 700 Mbps                                                                       | 1.55 |     |                   |     |                                    |      |       |

<sup>(1)</sup> Differential SSTL requires a  $V_{\text{REF}}$  input.

<sup>(1)</sup> Differential HSTL requires a  $V_{\text{REF}}$  input.

| Table 1-20. | Differential I/O Standar | d Specifications for Cyc | clone IV Devices (1) | (Part 2 of 2)—Preliminary |

|-------------|--------------------------|--------------------------|----------------------|---------------------------|

|-------------|--------------------------|--------------------------|----------------------|---------------------------|

| I/O Standard                      |       | V <sub>CCIO</sub> (V) |       | V <sub>ID</sub> (mV) |     |      | V <sub>IcM</sub> (V) <sup>(2)</sup>                                                                 |      |     |     | (3) | V <sub>0S</sub> (V) <sup>(3)</sup> |      |       |

|-----------------------------------|-------|-----------------------|-------|----------------------|-----|------|-----------------------------------------------------------------------------------------------------|------|-----|-----|-----|------------------------------------|------|-------|

| i/U Stailuaru                     | Min   | Тур                   | Max   | Min                  | Max | Min  | Condition                                                                                           | Max  | Min | Тур | Max | Min                                | Тур  | Max   |

| LVDS                              |       |                       |       |                      |     | 0.05 | $D_{MAX} \leq 500 \text{ Mbps}$                                                                     | 1.80 |     |     |     |                                    |      |       |

| (Column<br>I/Os)                  | 2.375 | 2.5                   | 2.625 | 100                  | _   | 0.55 | $\begin{array}{l} 500 \; \text{Mbps} \leq D_{\text{MAX}} \\ \leq \; 700 \; \text{Mbps} \end{array}$ | 1.80 | 247 | _   | 600 | 1.125                              | 1.25 | 1.375 |

| 1, 33)                            |       |                       |       |                      |     | 1.05 | $D_{MAX} > 700 \text{ Mbps}$                                                                        | 1.55 |     |     |     |                                    |      |       |

| BLVDS (Row I/Os) (4)              | 2.375 | 2.5                   | 2.625 | 100                  |     | _    | _                                                                                                   | _    | _   | _   | _   |                                    |      | _     |

| BLVDS<br>(Column<br>I/Os) (4)     | 2.375 | 2.5                   | 2.625 | 100                  |     | _    | _                                                                                                   | _    | _   | _   | _   | _                                  | _    | _     |

| mini-LVDS<br>(Row I/Os)           | 2.375 | 2.5                   | 2.625 | _                    | _   | _    | _                                                                                                   | _    | 300 | _   | 600 | 1.0                                | 1.2  | 1.4   |

| mini-LVDS<br>(Column<br>I/Os) (5) | 2.375 | 2.5                   | 2.625 | _                    | _   | _    | _                                                                                                   | _    | 300 | _   | 600 | 1.0                                | 1.2  | 1.4   |

| RSDS® (Row I/Os) (5)              | 2.375 | 2.5                   | 2.625 | _                    |     | _    | _                                                                                                   | _    | 100 | 200 | 600 | 0.5                                | 1.2  | 1.5   |

| RSDS<br>(Column<br>I/Os) (5)      | 2.375 | 2.5                   | 2.625 | _                    | _   | _    | _                                                                                                   | _    | 100 | 200 | 600 | 0.5                                | 1.2  | 1.5   |

| PPDS (Row I/Os) (5)               | 2.375 | 2.5                   | 2.625 | _                    | _   | _    | _                                                                                                   | _    | 100 | 200 | 600 | 0.5                                | 1.2  | 1.4   |

| PPDS<br>(Column<br>I/Os) (5)      | 2.375 | 2.5                   | 2.625 | _                    | _   | _    | _                                                                                                   |      | 100 | 200 | 600 | 0.5                                | 1.2  | 1.4   |

#### Notes to Table 1-20:

- (1) For an explanation of terms used in Table 1–20, refer to "Glossary" on page 1–38.

- (2)  $V_{IN}$  range:  $0 \text{ V} \leq V_{IN} \leq 1.85 \text{ V}$ .

- (3)  $R_L$  range:  $90 \le R_L \le 110 \Omega$ .

- (4) There are no fixed  $V_{IN}$ ,  $V_{OD}$ , and  $V_{OS}$  specifications for BLVDS. They depend on the system topology.

- (5) The Mini-LVDS, RSDS, and PPDS standards are only supported at the output pins.

- (6) The LVPECL I/O standard is only supported on dedicated clock input pins. This I/O standard is not supported for output pins.

## **Power Consumption**

Use the following methods to estimate power for a design:

- the Excel-based EPE

- the Quartus<sup>®</sup> II PowerPlay power analyzer feature

The interactive Excel-based EPE is used prior to designing the device to get a magnitude estimate of the device power. The Quartus II PowerPlay power analyzer provides better quality estimates based on the specifics of the design after place-and-route is complete. The PowerPlay power analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, combined with detailed circuit models, can yield very accurate power estimates.

For more information about power estimation tools, refer to the *Early Power Estimator User Guide* and the *PowerPlay Power Analysis* chapter in volume 3 of the *Quartus II Handbook*.

## **Switching Characteristics**

This section provides performance characteristics of Cyclone IV core and periphery blocks for commercial grade devices.

These characteristics can be designated as Preliminary or Final.

- Preliminary characteristics are created using simulation results, process data, and other known parameters. The upper-right hand corner of these tables show the designation as "Preliminary".

- Final numbers are based on actual silicon characterization and testing. The numbers reflect the actual performance of the device under worst-case silicon process, voltage, and junction temperature conditions. There are no designations on finalized tables.

## **Transceiver Performance Specifications**

Table 1–21 lists the Cyclone IV GX transceiver specifications.

Table 1-21. Transceiver Specification for Cyclone IV GX Devices (Part 1 of 4)—Preliminary

| Symbol/                                                   | O a walking a                                             |                     | C6            |           |                     | C7, I7        |            |                     |               | Unit   |        |

|-----------------------------------------------------------|-----------------------------------------------------------|---------------------|---------------|-----------|---------------------|---------------|------------|---------------------|---------------|--------|--------|

| Description                                               | Conditions                                                | Min                 | Тур           | Max       | Min                 | Тур           | Max        | Min                 | Тур           | Max    | Unit   |

| Reference Clock                                           |                                                           |                     |               |           |                     |               |            |                     |               |        |        |

| Supported I/O<br>Standards                                |                                                           | 1.2 V F             | PCML, 1.5     | V PCML, 3 | .3 V PCN            | IL, Differe   | ntial LVPE | CL, LVD             | S, HCSL       |        |        |

| Input frequency from REFCLK input pins                    | _                                                         | 50                  | _             | 156.25    | 50                  | _             | 156.25     | 50                  | _             | 156.25 | MHz    |

| Spread-spectrum<br>modulating clock<br>frequency          | Physical interface<br>for PCI Express<br>(PIPE) mode      | 30                  | _             | 33        | 30                  | _             | 33         | 30                  | _             | 33     | kHz    |

| Spread-spectrum downspread                                | PIPE mode                                                 | _                   | 0 to<br>-0.5% | _         | _                   | 0 to<br>-0.5% | _          | _                   | 0 to<br>-0.5% | _      | _      |

| V <sub>ICM</sub> (AC coupled)                             |                                                           |                     | 1100 ± 5      | 5%        |                     | 1100 ± 5%     | <b>%</b>   |                     | 1100 ± 5      | %      | mV     |

| V <sub>ICM</sub> (DC coupled)                             | HCSL I/O<br>standard for PCIe<br>reference clock          | 250                 | _             | 550       | 250                 | _             | 550        | 250                 | _             | 550    | mV     |

| Transmitter REFCLK<br>Phase Noise <sup>(1)</sup>          | Frequency offset                                          | _                   | _             | -123      | _                   | _             | -123       | _                   | _             | -123   | dBc/Hz |

| Transmitter REFCLK<br>Total Jitter <sup>(1)</sup>         | = 1 MHz – 8 MHZ                                           | _                   | _             | 42.3      | _                   | _             | 42.3       | _                   | _             | 42.3   | ps     |

| R <sub>ref</sub>                                          | _                                                         | _                   | 2000<br>± 1%  | _         | _                   | 2000<br>± 1%  | _          | _                   | 2000<br>± 1%  | _      | Ω      |

| Transceiver Clock                                         |                                                           |                     |               |           |                     |               |            |                     |               |        |        |

| cal_blk_clk clock frequency                               | _                                                         | 10                  | _             | 125       | 10                  | _             | 125        | 10                  | _             | 125    | MHz    |

| fixedclk Clock<br>frequency                               | PCIe Receiver<br>Detect                                   | _                   | 125           | _         | _                   | 125           | _          | _                   | 125           | _      | MHz    |

| reconfig_clk<br>clock frequency                           | Dynamic<br>reconfiguration<br>clock frequency             | 2.5/<br>37.5<br>(2) | _             | 50        | 2.5/<br>37.5<br>(2) | _             | 50         | 2.5/<br>37.5<br>(2) | _             | 50     | MHz    |

| Delta time between reconfig_clk                           | _                                                         | _                   | _             | 2         | _                   | _             | 2          | _                   | _             | 2      | ms     |

| Transceiver block<br>minimum<br>power-down pulse<br>width | _                                                         |                     | 1             | -         | _                   | 1             | _          |                     | 1             | _      | μѕ     |

| Receiver                                                  |                                                           |                     |               |           |                     | _             |            |                     |               |        |        |

| Supported I/O<br>Standards                                | 1.4 V PCML,<br>1.5 V PCML,<br>2.5 V PCML,<br>LVPECL, LVDS |                     |               |           |                     |               |            |                     |               |        |        |

Table 1–21. Transceiver Specification for Cyclone IV GX Devices (Part 2 of 4)—Preliminary

| Symbol/                                                                                        | Oanditions                                                                     |      | C6           |                               |      | C7, I7                 |                                  | C8   |              |                                  |      |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|--------------|-------------------------------|------|------------------------|----------------------------------|------|--------------|----------------------------------|------|

| Description                                                                                    | Conditions                                                                     | Min  | Тур          | Max                           | Min  | Тур                    | Max                              | Min  | Тур          | Max                              | Unit |

| Data rate (F324 and smaller package)                                                           | _                                                                              | 600  | _            | 2500                          | 600  | _                      | 2500                             | 600  | _            | 2500                             | Mbps |

| Data rate (F484 and larger package)                                                            | _                                                                              | 600  | _            | 3125                          | 600  | _                      | 3125                             | 600  | _            | 2500                             | Mbps |

| Absolute V <sub>MAX</sub> for a receiver pin <sup>(3)</sup>                                    | _                                                                              | _    | _            | 1.6                           | _    | _                      | 1.6                              | _    | _            | 1.6                              | V    |

| Operational V <sub>MAX</sub> for a receiver pin                                                | _                                                                              | _    | _            | 1.5                           | _    | _                      | 1.5                              | _    | _            | 1.5                              | V    |

| Absolute V <sub>MIN</sub> for a receiver pin                                                   | _                                                                              | -0.4 | _            | _                             | -0.4 | _                      | _                                | -0.4 | _            | _                                | V    |

| Peak-to-peak<br>differential input<br>voltage V <sub>ID</sub> (diff p-p)                       | V <sub>ICM</sub> = 0.82 V<br>setting, Data Rate<br>= 600 Mbps to<br>3.125 Gbps | 0.1  | _            | 2.7                           | 0.1  | _                      | 2.7                              | 0.1  | _            | 2.7                              | V    |

| V <sub>ICM</sub>                                                                               | V <sub>ICM</sub> = 0.82 V<br>setting                                           | _    | 820 ±<br>10% | _                             | _    | 820 ±<br>10%           | _                                | _    | 820 ±<br>10% | _                                | mV   |

| Differential on-chip                                                                           | 100–Ω setting                                                                  | _    | 100          | _                             | _    | 100                    | _                                | _    | 100          | _                                | Ω    |

| termination resistors                                                                          | 150– $\Omega$ setting                                                          |      | 150          | _                             | _    | 150                    | _                                | _    | 150          | _                                | Ω    |

| Differential and common mode return loss                                                       | PIPE, Serial<br>Rapid I/O SR,<br>SATA, CPRI LV,<br>SDI, XAUI                   |      |              |                               |      | Compliant              | t                                |      |              |                                  | _    |

| Programmable ppm detector <sup>(4)</sup>                                                       | _                                                                              |      |              |                               |      | , 100, 125<br>250, 300 |                                  |      |              |                                  | ppm  |