## Buck Converter - Low Voltage, Dual, Output 2.1 MHz

# NCV896530

The NCV896530 dual step-down dc-dc converter is a monolithic integrated circuit dedicated to automotive driver information systems from a downstream voltage rail.

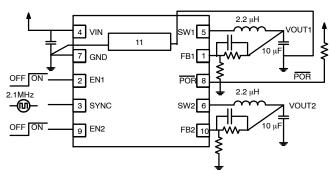

Both channels are externally adjustable from 0.9 V to 3.3 V and can source totally up to 1600 mA. Converters are running at 2.1 MHz switching frequency above the sensitive AM band and operate  $180^{\circ}$  out of phase to reduce large amounts of current demand on the rail. Synchronous rectification offers improved system efficiency.

The NCV896530 provides additional features expected in automotive power systems such as integrated soft–start, hiccup mode current limit and thermal shutdown protection. The device can also be synchronized to an external clock signal in the range of 2.1 MHz.

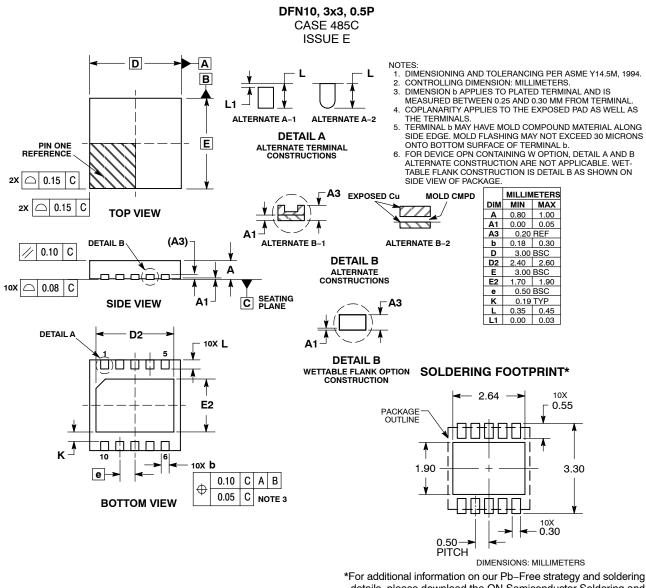

The NCV896530 is available in a space saving, 3 x 3 mm 10-pin DFN package.

#### Features

- Synchronous Rectification for Higher Efficiency

- 2.1 MHz Switching Frequency, 180° Out-of-Phase

- Sources up to 1600 mA Total and 1 A Per Channel

- Adjustable Output Voltage from 0.9 V to 3.3 V

- 2.7 V to 5.5 V Input Voltage Range

- Thermal Limit and Short Circuit Protection

- Auto Synchronizes with an External Clock

- Wettable Flanks DFN

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC–Q100 Qualified and PPAP Capable

- This is a Pb–Free Device

#### **Typical Applications**

- Audio

- Infotainment

- Vision System

- Instrumentation

Figure 1. NCV896530 Typical Application

## **ON Semiconductor®**

www.onsemi.com

## **ORDERING INFORMATION**

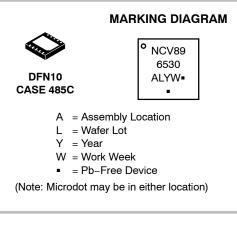

See detailed ordering, marking and shipping information on page 8 of this data sheet.

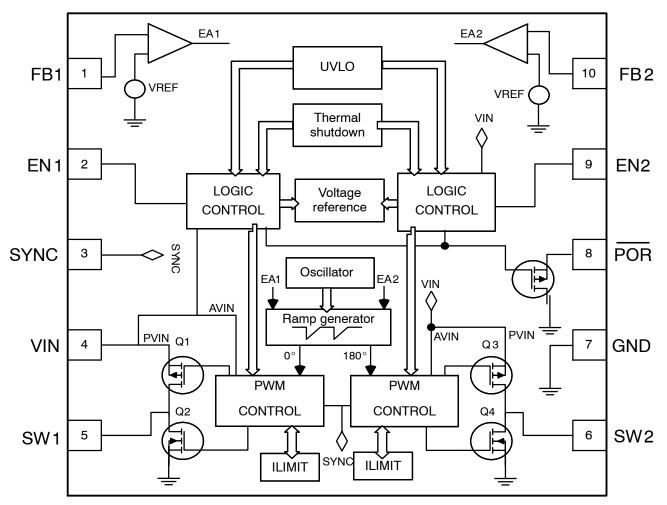

## **BLOCK DIAGRAM**

Figure 2. Simplified Block Diagram

### **PIN FUNCTION DESCRIPTION**

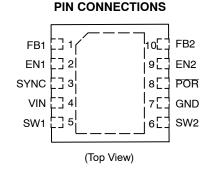

| Pin | Pin Name    | Туре                    | Description                                                                                                                                                                                                                                                                                    |  |  |  |

|-----|-------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1   | FB1         | Analog Input            | Feedback voltage from the output 1. This is the input to the error amplifier.                                                                                                                                                                                                                  |  |  |  |

| 2   | EN1         | Digital Input           | Enable for converter 1. This pin is active HIGH (equal or lower Analog Input voltage<br>and is turned off by logic LOW.<br>Do not let this pin float.                                                                                                                                          |  |  |  |

| 3   | SYNC        | Digital Input           | Oscillator Synchronization. This pin can be synchronized to an external clock in the range of 2.1 MHz. If not used, the pin must to be connected to ground.                                                                                                                                    |  |  |  |

| 4   | VIN         | Analog / Power<br>Input | Power supply input for the PFET power stage, analog and digital blocks. The pin must be decoupled to ground by a 10 $\mu F$ ceramic capacitor.                                                                                                                                                 |  |  |  |

| 5   | SW1         | Analog Output           | Connection from power MOSFETs of output 1 to the Inductor.                                                                                                                                                                                                                                     |  |  |  |

| 6   | SW2         | Analog Output           | Connection from power MOSFETs of output 2 to the Inductor.                                                                                                                                                                                                                                     |  |  |  |

| 7   | GND         | Analog Ground           | This pin is the GROUND reference for the analog section of the IC. The pin must be connected to the system ground.                                                                                                                                                                             |  |  |  |

| 8   | POR         | Digital Output          | Power On Reset. This is an open drain output. This output is shutting down when one of the output voltages are less than 90% (typ) of their nominal values. A pull-up resistor around 500 k $\Omega$ should be connected between POR and VIN, VOUT1 or VOUT2 depending on the supplied device. |  |  |  |

| 9   | EN2         | Digital Input           | Enable for converter 2. This pin is active HIGH (equal or lower Analog Input voltage) and is turned off by logic LOW. Do not let this pin float.                                                                                                                                               |  |  |  |

| 10  | FB2         | Analog Input            | Feedback voltage from the output 2. This is the input to the error amplifier.                                                                                                                                                                                                                  |  |  |  |

| 11  | Exposed Pad | Power Ground            | This pin is the GROUND reference for the NFET power stage of the IC. The pin must be connected to the system ground and to both input and output capacitors.                                                                                                                                   |  |  |  |

### MAXIMUM RATINGS

| Rating                                                     | Symbol           | Value      | Unit    |

|------------------------------------------------------------|------------------|------------|---------|

| Minimum Voltage All Pins                                   | V <sub>min</sub> | -0.3       | V       |

| Maximum Voltage All Pins                                   | V <sub>max</sub> | 6.0        | V       |

| Maximum Voltage ENx, SYNC, FBx, , SWx, POR                 | V <sub>max</sub> | VIN+0.3    | V       |

| Thermal Resistance Junction-to-Ambient (3x3 DFN) (Note 1)  | $R_{	hetaJA}$    | 40         | °C/W    |

| Storage Temperature Range                                  | T <sub>stg</sub> | -55 to 150 | °C      |

| Junction Operating Temperature                             | TJ               | -40 to 150 | °C      |

| ESD Withstand Voltage<br>Human Body Model<br>Machine Model | V <sub>esd</sub> | 2.0<br>200 | kV<br>V |

| Moisture Sensitivity Level                                 | MSL              | 3          | per IPC |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected. 1. Mounted on 1 sq. in. of a 4-layer PCB with 1 oz. copper thickness.

| <b>ELECTRICAL CHARACTERISTICS</b> (2.7 V < V <sub>IN</sub> < 5.5 V, Min and Max values are valid for the temperature range $-40^{\circ}C \le T_J \le 10^{\circ}$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| +150°C unless noted otherwise, and are guaranteed by test design or statistical correlation, Typical values are referenced to $T_A = +25$ °C)                    |

| ,                                | 0 , 0                                                                          |                      |     |         |         |            |

|----------------------------------|--------------------------------------------------------------------------------|----------------------|-----|---------|---------|------------|

| Rating                           | Conditions                                                                     | Symbol               | Min | Тур     | Max     | Unit       |

| INPUT VOLTAGE                    |                                                                                |                      |     |         | <b></b> |            |

| Quiescent Current                | SYNC = GND, $V_{FB}$ = 0 V<br>EN1 = EN2 = 2 V, No Switching                    | Ι <sub>Q</sub>       | -   | 2.0     | 3.0     | mA         |

| Standby Current                  | EN1 = EN2 = 0 V                                                                | I <sub>STBMAX</sub>  | -   | 4.0     | 10      | μA         |

| Under Voltage Lockout            | V <sub>IN</sub> falling                                                        | V <sub>UVLO</sub>    | 2.2 | 2.4     | 2.6     | V          |

| Under Voltage Hysteresis         |                                                                                | V <sub>UVLOH</sub>   | -   | 100     | 150     | mV         |

| SYNC                             |                                                                                | -                    | •   |         | •       |            |

| SYNC Threshold Voltage           | Logic high                                                                     | VIHSYNC              | 1.2 | -       | -       | V          |

|                                  | Logic Low                                                                      | VILSYNC              |     |         | 0.4     |            |

| SYNC Pin Bias Current            | V <sub>SYNC</sub> = 5 V                                                        | IILSYNC              | 2   |         | 50      | μA         |

| External Synchronization         |                                                                                | F <sub>SYNC</sub>    | 1.8 |         | 2.7     | MHz        |

| SYNC Pulse Duty Ratio            |                                                                                | T <sub>SYNC</sub>    |     | 50      |         | %          |

| EN1, EN2                         |                                                                                |                      |     |         |         |            |

| ENx Threshold Voltage            | Logic high                                                                     | VIHENx               | 1.2 | -       | -       | V          |

|                                  | Logic Low                                                                      | VILENx               |     |         | 0.4     |            |

| ENx Pin Bias Current             | V <sub>ENx</sub> = 5 V                                                         | I <sub>ILENx</sub>   | 2   |         | 50      | μA         |

| POWER ON RESET                   |                                                                                |                      |     |         |         |            |

| Power On Reset Threshold         | V <sub>OUT</sub> falling                                                       | V <sub>PORT</sub>    | 87% |         | 93%     | V          |

| Power On Reset Hysteresis        |                                                                                | V <sub>PORH</sub>    | _   |         | 3%      | V          |

| Sink Current                     | V <sub>POR</sub> = 0.4 V                                                       | I <sub>SIPOR</sub>   | 2   |         |         | mA         |

| OUTPUT PERFORMANCES              |                                                                                | 0 011                |     |         |         |            |

| Feedback Voltage Threshold       | FB1, FB2                                                                       | V <sub>FB</sub>      | -   | 0.6     | -       | V          |

| Feedback Voltage Accuracy        | T <sub>A</sub> = 25C                                                           | ΔV <sub>OUT</sub>    |     | ±1      | _       | %          |

|                                  | -40°C < T <sub>A</sub> < 125°C                                                 | ΔV <sub>OUT</sub>    | -2  | _       | +2      |            |

| Soft-Start Time                  | Time from EN to 90% of output voltage                                          | t <sub>START</sub>   | 400 | _       | 1000    | μS         |

| Switching Frequency              | EN1 = EN2 = 1, V <sub>IN</sub> = 5 V                                           | F <sub>SW</sub>      | 1.8 | 2.1     | 2.6     | MHz        |

| Duty Cycle                       |                                                                                | D                    | -   | _       | 100     | %          |

| POWER SWITCHES                   |                                                                                |                      |     |         |         |            |

| High-Side MOSFET On-resistance   | I <sub>RDS(on)</sub> = 600 mA, V <sub>IN</sub> = 5 V, T <sub>A</sub> = 25°C    | R <sub>ONHS</sub>    | -   | 500     | 820     | mΩ         |

| Low-Side MOSFET On-resistance    | $I_{RDS(on)} = 600 \text{ mA}, V_{IN} = 5 \text{ V}, T_A = 25^{\circ}\text{C}$ | R <sub>ONLS</sub>    | _   | 450     | 820     | mΩ         |

| High-Side MOSFET Leakage Current | $V_{IN} = 5 V, V_{LX} = 0 V, V_{ENx} = 0 V$                                    | ILEAKHS              | _   |         | 5       | μA         |

| Low-Side MOSFET Leakage Current  | $V_{LX} = 5 \text{ V},  \text{V}_{\text{ENX}} = 0 \text{ V}$                   | ILEAKLS              | _   |         | 5       | μ <b>Α</b> |

| Minimum On Time                  |                                                                                | T <sub>ONMIN</sub>   | _   | ł – – – | 80      | ns         |

| PROTECTION                       |                                                                                | ONNIN                |     |         |         |            |

| Current Limit                    | Peak inductor current, V <sub>IN</sub> = 5 V,<br>100% duty cycle               | I <sub>PK</sub>      | 1.4 |         | 2.0     | A          |

| Thermal Shutdown Threshold       |                                                                                | T <sub>SD</sub>      | 150 | 170     | 190     | °C         |

| Thermal Shutdown Hysteresis      |                                                                                | T <sub>SDH</sub>     | 5   |         | 20      | °C         |

| Hiccup Time                      | % of Soft–Start Time                                                           | t <sub>hcp,dly</sub> | ł   | 60      |         | %          |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

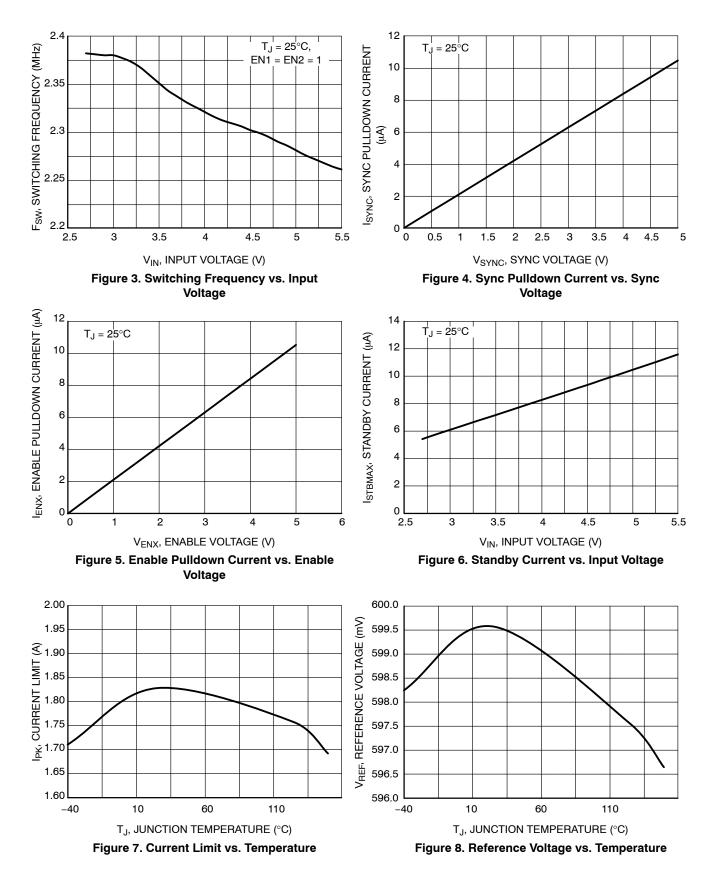

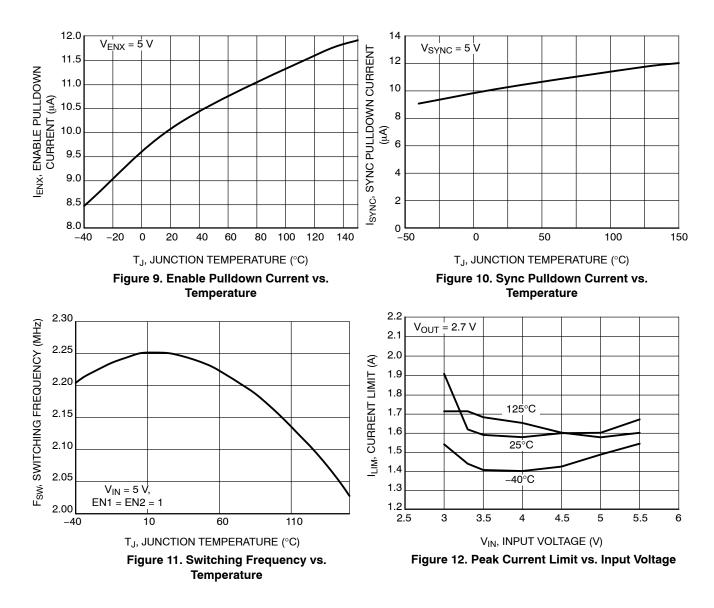

## **TYPICAL CHARACTERISTICS CURVES**

## **TYPICAL CHARACTERISTICS CURVES**

#### **DC/DC OPERATION DESCRIPTION**

#### **PWM Operating Mode**

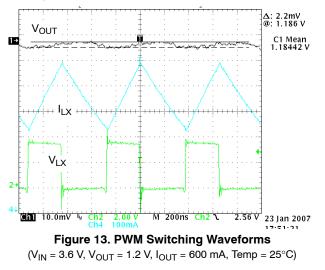

The output voltage of the device is regulated by modulating the on-time pulse width of the main switch Q1 at a fixed 2.1 MHz frequency (Figure 13).

The switching of the PMOS Q1 is controlled by a flip–flop driven by the internal oscillator and a comparator that compares the error signal from an error amplifier with the sum of the sensed current signal and compensation ramp.

The driver switches ON and OFF the upper side transistor (Q1) and switches the lower side transistor in either ON state or in current source mode.

At the beginning of each cycle, the main switch Q1 is turned ON by the rising edge of the internal oscillator clock. The inductor current ramps up until the sum of the current sense signal and compensation ramp becomes higher than the error amplifier's voltage. Once this has occurred, the PWM comparator resets the flip–flop, Q1 is turned OFF while the synchronous switch Q2 is turned in its current source mode. Q2 replaces the external Schottky diode to reduce the conduction loss and improve the efficiency. To avoid overall power loss, a certain amount of dead time is introduced to ensure Q1 is completely turned OFF before Q2 is being turned ON.

#### Soft-Start

The NCV896530 uses soft start to limit the inrush current when the device is initially powered up or enabled. Soft start is implemented by gradually increasing the reference voltage until it reaches the full reference voltage. During startup, a pulsed current source charges the internal soft start capacitor to provide gradually increasing reference voltage. When the voltage across the capacitor ramps up to the nominal reference voltage, the pulsed current source will be switched off and the reference voltage will switch to the regular reference voltage.

#### **Over Current Hiccup Protection**

When the current through the inductor exceeds the current limit the NCV896530 enters over current hiccup mode.

When an over current event is detected the NCV896530 disables the outputs and attempts to re-enable the outputs after the hiccup time. The part remains off for the hiccup time and then goes through the power on reset procedure. If the excessive load has been removed then the output stage re-enables and operates normally; however, if the excessive load is still present the cycle begins again. Internal heat dissipation is kept to a minimum as current will only flow during the reset time of the protection circuitry. The hiccup mode is continuous until the excessive load is removed.

#### Low Dropout Operation

The NCV896530 offers a low input-to-output voltage difference. The NCV896530 can operate at 100% duty cycle on both channels.

In this mode the PMOS (Q1) remains completely ON. The minimum input voltage to maintain regulation can be calculated as:

$$V_{IN(min)} = V_{OUT(max)} + \left(I_{OUT} \times \left(R_{DS(on)} + R_{INDUCTOR}\right)\right)$$

(eq. 1)

V<sub>OUT</sub>: Output Voltage I<sub>OUT</sub>: Max Output Current R<sub>DS</sub>(ON): P-Channel Switch R<sub>DS(on)</sub> R<sub>INDUCTOR</sub>: Inductor Resistance (DCR)

#### **Power On Reset**

The Power On Reset (POR) is pulled low when one of the converter is out of 90% of the regulation. When both outputs are in the range of regulation. If only one channel is active, POR stays low. When the inactive regulator becomes enabled, POR is kept low until the output reaches its voltage range. A pull–up resistor is needed to this open drain output. The resistor may be connected to VIN or to an output voltage of one regulator if the device supplied can not accept VIN on the IO. POR is low when NCV896530 is off. Leave the POR pin unconnected when not used.

#### **Frequency Synchronization**

The NCV896530 can be synchronized with an external clock signal by using the SYNC pin (1.8 MHz – 2.4 MHz). During synchronization, the outputs are in phase.

#### **Thermal Shutdown**

Internal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. If the junction temperature exceeds  $T_{SD}$ , the device shuts down. In this mode all power transistors and control circuits are turned off. The device restarts in soft start after the temperature drops below 130°C min. This feature is provided to prevent catastrophic failures from accidental device overheating.

## **Switching Frequency**

When switcher 2 is enabled and switcher 1 is disabled, the switching frequency is approximately 120 kHz higher than when switcher 1 is enabled and switcher 2 is either enabled or disabled.

### **Conversion Ratio**

The minimum conversion ratio is dictated by switching frequency and the minimum on time. The minimum achievable output is:

$$V_{OUT} = 0.2 \times V_{IN}$$

### **Maximum Output Capacitance**

The maximum output capacitance is determined by the amount the capacitor can be charged during soft start and the

effect on the control loop. If more than 100  $\mu$ F is used on an output small signal analysis should be done to make sure that sufficient phase margin is maintained. The maximum allowable due to soft start current limit is given by the following equation:

$$C_{max} = \frac{I_{OUT, startup} t_{start}}{V_{OUT}}$$

(eq. 2)

C<sub>max</sub>: Maximum output capacitance (F) I<sub>OUT,startup</sub>: Output current during soft start (A) t<sub>start</sub>: Soft-start time (s) V<sub>out</sub>: Regulated output voltage (V)

## **DEVICE ORDERING INFORMATION**

| Device          | Status              | Part Marking   | Package            | Shipping <sup>†</sup> |

|-----------------|---------------------|----------------|--------------------|-----------------------|

| NCV896530MWATXG | Recommended         | NCV89<br>6530A | DFN10<br>(Pb–Free) | 3000 / Tape & Reel    |

| NCV896530MWTXG  | Not for new designs | NCV89<br>6530  | DFN10<br>(Pb-Free) | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

#### PACKAGE DIMENSIONS

Aror additional information on our PD-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor products are not application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconducts products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal inj

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative