## P-Channel 1.8 V (G-S) MOSFET

| PRODUCT SUMMARY     |                                    |                    |  |  |

|---------------------|------------------------------------|--------------------|--|--|

| V <sub>DS</sub> (V) | $R_{DS(on)}(\Omega)$               | I <sub>D</sub> (A) |  |  |

|                     | 0.125 at V <sub>GS</sub> = - 4.5 V | ± 1.8              |  |  |

| - 8                 | 0.160 at V <sub>GS</sub> = - 2.5 V | ± 1.6              |  |  |

|                     | 0.210 at V <sub>GS</sub> = - 1.8 V | ± 1.4              |  |  |

#### **FEATURES**

- Halogen-free According to IEC 61249-2-21 Definition

- TrenchFET® Power MOSFET: 1.8 V Rated

- Compliant to RoHS Directive 2002/95/EC

Ordering Information: Si1405DL-T1-E3 (Lead (Pb)-free)

Si1405DL-T1-GE3 (Lead (Pb)-free and Halogen-free)

| <b>ABSOLUTE MAXIMUM RATINGS</b> T <sub>A</sub> = 25 °C, unless otherwise noted |                        |                                   |              |        |    |  |

|--------------------------------------------------------------------------------|------------------------|-----------------------------------|--------------|--------|----|--|

| Parameter                                                                      | Symbol                 | 5 s                               | Steady State | Unit   |    |  |

| Drain-Source Voltage                                                           |                        | V <sub>DS</sub>                   | - 8          |        | ٧  |  |

| Gate-Source Voltage                                                            |                        | V <sub>GS</sub>                   | ± 8          |        |    |  |

| Continuous Drain Current (T <sub>J</sub> = 150 °C) <sup>a</sup>                | T <sub>A</sub> = 25 °C | - I <sub>D</sub>                  | ± 1.8        | ± 1.6  | A  |  |

|                                                                                | T <sub>A</sub> = 85 °C |                                   | ± 1.5        | ± 1.2  |    |  |

| Pulsed Drain Current                                                           |                        | I <sub>DM</sub>                   | ± 5          |        | A  |  |

| Continuous Diode Current (Diode Conduction) <sup>a</sup>                       |                        | I <sub>S</sub>                    | - 0.8        | - 0.8  |    |  |

| Maximum Power Dissipation <sup>a</sup>                                         | T <sub>A</sub> = 25 °C | P <sub>D</sub>                    | 0.625        | 0.568  | W  |  |

| waxiinum rowei Dissipation                                                     | T <sub>A</sub> = 85 °C |                                   | 0.400        | 0.295  |    |  |

| Operating Junction and Storage Temperature Range                               |                        | T <sub>J</sub> , T <sub>stg</sub> | - 55         | to 150 | °C |  |

| THERMAL RESISTANCE RATINGS               |              |                   |         |      |      |  |

|------------------------------------------|--------------|-------------------|---------|------|------|--|

| Parameter                                | Symbol       | Typical           | Maximum | Unit |      |  |

| Maximum Junction-to-Ambient <sup>a</sup> | t ≤ 5 s      | R <sub>thJA</sub> | 165     | 200  |      |  |

| Maximum Junction-to-Ambient              | Steady State |                   | 180     | 220  | °C/W |  |

| Maximum Junction-to-Foot (Drain)         | Steady State | R <sub>thJF</sub> | 105     | 130  |      |  |

#### Note:

a. Surface mounted on 1" x 1" FR4 board.

## Vishay Siliconix

| Parameter                                     | Symbol              | Test Conditions                                                                 | Min.   | Тур.   | Max.  | Unit |  |

|-----------------------------------------------|---------------------|---------------------------------------------------------------------------------|--------|--------|-------|------|--|

| Static                                        |                     |                                                                                 |        |        |       |      |  |

| Gate Threshold Voltage                        | V <sub>GS(th)</sub> | $V_{DS} = V_{GS}, I_{D} = -250 \mu A$                                           | - 0.45 |        |       | V    |  |

| Gate-Body Leakage                             | I <sub>GSS</sub>    | $V_{DS} = 0 \text{ V}, V_{GS} = \pm 8 \text{ V}$                                |        |        | ± 100 | nA   |  |

| Zava Cata Valtaga Dvain Curvant               | _                   | V <sub>DS</sub> = - 6.4 V, V <sub>GS</sub> = 0 V                                |        |        | - 1   | μΑ   |  |

| Zero Gate Voltage Drain Current               | I <sub>DSS</sub>    | $V_{DS} = -6.4 \text{ V}, V_{GS} = 0 \text{ V}, T_{J} = 85 ^{\circ}\text{C}$    |        |        | - 5   |      |  |

| On-State Drain Current <sup>a</sup>           | I <sub>D(on)</sub>  | V <sub>DS</sub> = - 5 V, V <sub>GS</sub> = - 4.5 V                              | - 2    |        |       | Α    |  |

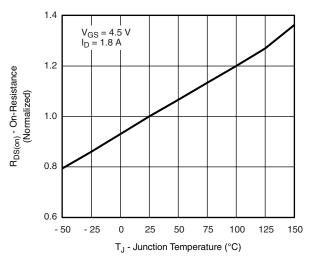

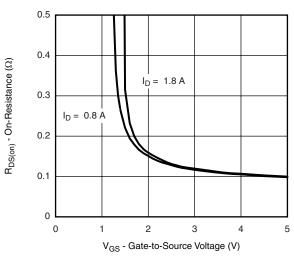

|                                               |                     | V <sub>GS</sub> = - 4.5 V, I <sub>D</sub> = - 1.8 A                             |        | 0.100  | 0.125 | 1    |  |

| Drain-Source On-State Resistance <sup>a</sup> | R <sub>DS(on)</sub> | V <sub>GS</sub> = - 2.5 V, I <sub>D</sub> = - 1.6 A                             |        | 0.130  | 0.160 | Ω    |  |

|                                               |                     | $V_{GS} = -1.8 \text{ V}, I_D = -0.8 \text{ A}$                                 |        | 0.170  | 0.210 | 1    |  |

| Forward Transconductance <sup>a</sup>         | 9 <sub>fs</sub>     | V <sub>DS</sub> = - 10 V, I <sub>D</sub> = - 1.8 A                              |        | 3.8    |       | S    |  |

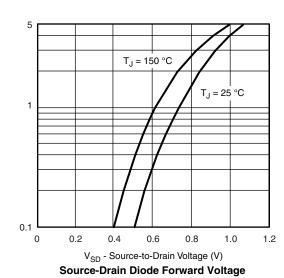

| Diode Forward Voltage <sup>a</sup>            | $V_{SD}$            | I <sub>S</sub> = - 0.8 A, V <sub>GS</sub> = 0 V                                 |        | - 0.76 | - 1.1 | V    |  |

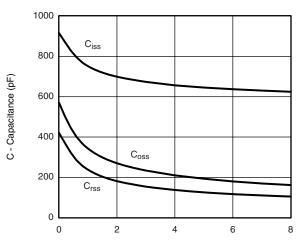

| Dynamic <sup>b</sup>                          |                     |                                                                                 |        |        |       |      |  |

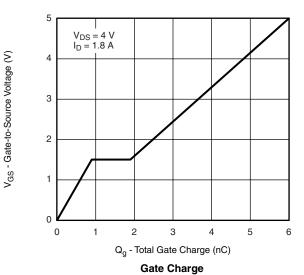

| Total Gate Charge                             | Qg                  |                                                                                 |        | 5.5    | 7.0   |      |  |

| Gate-Source Charge                            | Q <sub>gs</sub>     | $Q_{gs}$ $V_{DS} = -4 \text{ V}, V_{GS} = -4.5 \text{ V}, I_D = -1.8 \text{ A}$ |        | 0.9    |       | nC   |  |

| Gate-Drain Charge                             | $Q_{gd}$            |                                                                                 |        | 0.9    |       |      |  |

| Turn-On Delay Time                            | t <sub>d(on)</sub>  |                                                                                 |        | 8      | 12    |      |  |

| Rise Time                                     | t <sub>r</sub>      | $V_{DD}$ = - 4 V, $R_L$ = 10 $\Omega$                                           |        | 36     | 55    |      |  |

| Turn-Off Delay Time                           | t <sub>d(off)</sub> | $I_D \cong -1$ Å, $V_{GEN} = -4.5$ V, $R_g = 6$ $\Omega$                        |        | 33     | 50    | ns   |  |

| Fall Time                                     | t <sub>f</sub>      |                                                                                 |        | 30     | 45    |      |  |

| Source-Drain Reverse Recovery Time            | t <sub>rr</sub>     | I <sub>E</sub> = - 0.8 A, dI/dt = 100 A/μs                                      |        | 20     | 40    |      |  |

#### Notes:

- a. Pulse test; pulse width  $\leq 300~\mu s,$  duty cycle  $\leq 2~\%.$

- b. Guaranteed by design, not subject to production testing.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

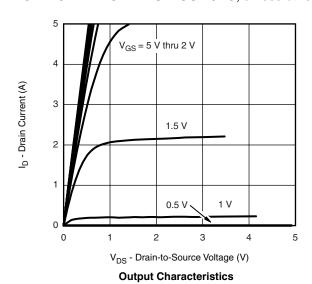

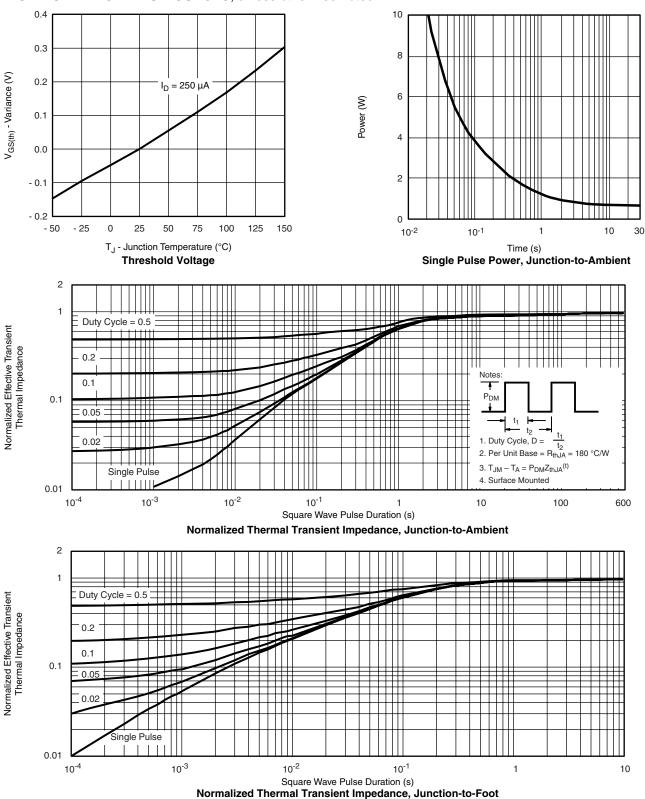

#### TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

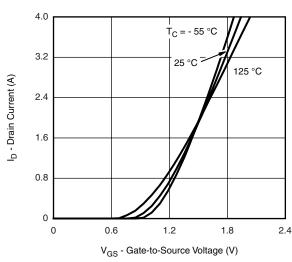

**Transfer Characteristics**

#### TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

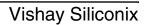

#### **On-Resistance vs. Drain Current**

V<sub>DS</sub> - Drain-to-Source Voltage (V)

#### On-Resistance vs. Junction Temperature

On-Resistance vs. Gate-to-Source Voltage

I<sub>S</sub> - Source Current (A)

### Vishay Siliconix

# VISHAY

#### TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see <a href="https://www.vishay.com/ppq?71073">www.vishay.com/ppq?71073</a>.

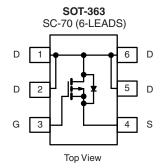

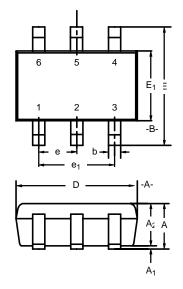

#### SC-70: 6-LEADS

|                                | MILLIMETERS |      |      | I        | NCHE  | S     |

|--------------------------------|-------------|------|------|----------|-------|-------|

| Dim                            | Min         | Nom  | Max  | Min      | Nom   | Max   |

| Α                              | 0.90        | -    | 1.10 | 0.035    | -     | 0.043 |

| <b>A</b> <sub>1</sub>          | _           | -    | 0.10 | _        | _     | 0.004 |

| A <sub>2</sub>                 | 0.80        | -    | 1.00 | 0.031    | _     | 0.039 |

| b                              | 0.15        | -    | 0.30 | 0.006    | _     | 0.012 |

| С                              | 0.10        | -    | 0.25 | 0.004    | -     | 0.010 |

| D                              | 1.80        | 2.00 | 2.20 | 0.071    | 0.079 | 0.087 |

| Е                              | 1.80        | 2.10 | 2.40 | 0.071    | 0.083 | 0.094 |

| E <sub>1</sub>                 | 1.15        | 1.25 | 1.35 | 0.045    | 0.049 | 0.053 |

| е                              | 0.65BSC     |      |      | 0.026BSC |       | ;     |

| e <sub>1</sub>                 | 1.20        | 1.30 | 1.40 | 0.047    | 0.051 | 0.055 |

| L                              | 0.10        | 0.20 | 0.30 | 0.004    | 0.008 | 0.012 |

| ۵                              | 7°Nom       |      |      |          | 7°Nom |       |

| ECN: S-03946—Rev. B, 09-Jul-01 |             |      |      |          |       |       |

DWG: 5550

## Single-Channel LITTLE FOOT® SC-70 3-Pin and 6-Pin MOSFET Recommended Pad Pattern and Thermal Peformance

#### INTRODUCTION

This technical note discusses pin-outs, package outlines, pad patterns, evaluation board layout, and thermal performance for single-channel LITTLE FOOT power MOSFETs in the SC-70 package. These new Vishay Siliconix devices are intended for small-signal applications where a miniaturized package is needed and low levels of current (around 350 mA) need to be switched, either directly or by using a level shift configuration. Vishay provides these single devices with a range of on-resistance specifications and in both traditional 3-pin and new 6-pin versions. The new 6-pin SC-70 package enables improved on-resistance values and enhanced thermal performance compared to the 3-pin package.

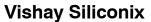

#### **PIN-OUT**

Figure 1 shows the pin-out description and Pin 1 identification for the single-channel SC-70 device in both 3-pin and 6-pin configurations. The pin-out of the 6-pin device allows the use of four pins as drain leads, which helps to reduce on-resistance and junction-to-ambient thermal resistance.

FIGURE 1.

For package dimensions see outline drawings: SC-70 (3-Leads) (http://www.vishay.com/doc?71153) SC-70 (6-Leads) (http://www.vishay.com/doc?71154)

#### **BASIC PAD PATTERNS**

See Application Note 826, Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs, (http://www.vishay.com/doc?72286) for the basic pad layout and dimensions for the 3-pin SC-70 and the 6-pin SC-70. These pad patterns are sufficient for the low-power applications for which this package is intended. Increasing the pad pattern has little effect on thermal resistance for the 3-pin device, reducing it by only 10% to 15%. But for the 6-pin device, increasing the pad patterns yields a reduction in thermal resistance on the order of 35% when using a 1-inch square with full copper on both sides of the printed circuit board (PCB). The availability of four drain leads rather than the traditional single drain lead allows a better thermal path from the package to the PCB and external environment.

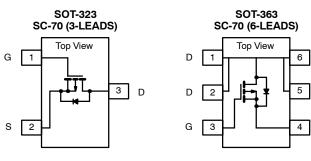

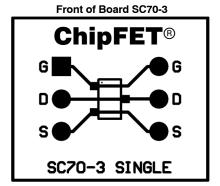

## EVALUATION BOARDS FOR THE SINGLE SC70-3 AND SC70-6

Figure 2 shows the 3-pin and 6-pin SC-70 evaluation boards (EVB). Both measure 0.6 inches by 0.5 inches. Their copper pad traces are the same as described in the previous section, *Basic Pad Patterns*. Both boards allow interrogation from the outer pins to 6-pin DIP connections, permitting test sockets to be used in evaluation testing.

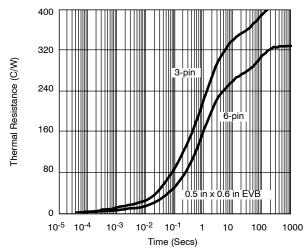

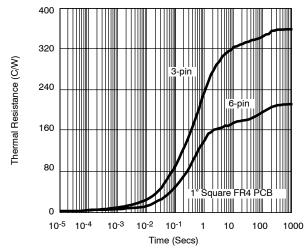

The thermal performance of the single SC-70 has been measured on the EVB for both the 3-pin and 6-pin devices, the results shown in Figures 3 and 4. The minimum recommended footprint on the evaluation board was compared with the industry standard of 1-inch square FR4 PCB with copper on both sides of the board.

ChipFET®

D

D

D

S

SC70-6 SINGLE

FIGURE 2.

Document Number: 71236 www.vishay.com

#### **Vishay Siliconix**

#### THERMAL PERFORMANCE

## Junction-to-Foot Thermal Resistance (the Package Performance)

Thermal performance for the 3-pin SC-70 measured as junction-to-foot thermal resistance is 285°C/W typical, 340°C/W maximum. Junction-to-foot thermal resistance for the 6-pin SC70-6 is 105°C/W typical, 130°C/W maximum — a nearly two-thirds reduction compared with the 3-pin device. The "foot" is the drain lead of the device as it connects with the body. This improved performance is obtained by the increase in drain leads from one to four on the 6-pin SC-70. Note that these numbers are somewhat higher than other LITTLE FOOT devices due to the limited thermal performance of the Alloy 42 lead-frame compared with a standard copper lead-frame.

## Junction-to-Ambient Thermal Resistance (dependent on PCB size)

The typical R $\theta_{JA}$ for the single 3-pin SC-70 is 360°C/W steady state, compared with 180°C/W for the 6-pin SC-70. Maximum ratings are 430°C/W for the 3-pin device versus 220°C/W for the 6-pin device. All figures are based on the 1-inch square FR4 test board. The following table shows how the thermal resistance impacts power dissipation for the two different pin-outs at two different ambient temperatures.

| SC-70 (3-PIN)                                                                                                 |                                                                                                               |

|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| Room Ambient 25 °C                                                                                            | Elevated Ambient 60 °C                                                                                        |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{360^{\circ}C/W}$ | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$ $P_{D} = \frac{150^{\circ}C - 60^{\circ}C}{360^{\circ}C/W}$ |

| $P_D = 347 \text{ mW}$                                                                                        | $P_D = 250 \text{ mW}$                                                                                        |

FIGURE 3. Comparison of SC70-3 and SC70-6 on EVB

| SC-70 (6-PIN)                                               |                                                             |

|-------------------------------------------------------------|-------------------------------------------------------------|

| Room Ambient 25 °C                                          | Elevated Ambient 60 °C                                      |

| $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           | $P_{D} = \frac{T_{J(max)} - T_{A}}{R\theta_{JA}}$           |

| $P_{D} = \frac{150^{\circ}C - 25^{\circ}C}{180^{\circ}C/W}$ | $P_{D} = \frac{150^{\circ}C - 60^{\circ}C}{180^{\circ}C/W}$ |

| $P_D = 694 \text{ mW}$                                      | $P_D = 500 \text{ mW}$                                      |

NOTE: Although they are intended for low-power applications, devices in the 6-pin SC-70 will handle power dissipation in excess of 0.5 W.

#### **Testing**

To aid comparison further, Figures 3 and 4 illustrate single-channel SC-70 thermal performance on two different board sizes and two different pad patterns. The results display the thermal performance out to steady state and produce a graphic account of the thermal performance variation between the two packages. The measured steady state values of  $R\theta_{JA}$  for the single 3-pin and 6-pin SC-70 are as follows:

| LITTLE FOOT SC-70                                                  |            |           |  |  |  |

|--------------------------------------------------------------------|------------|-----------|--|--|--|

|                                                                    | 3-Pin      | 6-Pin     |  |  |  |

| Minimum recommended pad pattern (see Figure 4) on the EVB.         | 410.31°C/W | 329.7°C/W |  |  |  |

| 2) Industry standard 1" square PCB with maximum copper both sides. | 360°C/W    | 211.8°C/W |  |  |  |

The results show that designers can reduce thermal resistance  $R\theta_{JA}$  on the order of 20% simply by using the 6-pin device rather than the 3-pin device. In this example, a  $80^{\circ}$ C/W reduction was achieved without an increase in board area. If increasing board size is an option, a further  $118^{\circ}$ C/W reduction could be obtained by utilizing a 1-inch square PCB area.

FIGURE 4. Comparison of SC70-3 and SC70-6 on 1" Square FR4 PCB

www.vishay.com Document Number: 71236

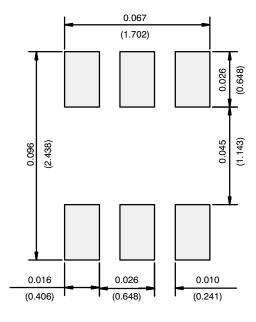

#### **RECOMMENDED MINIMUM PADS FOR SC-70: 6-Lead**

Recommended Minimum Pads Dimensions in Inches/(mm)

Return to Index

#### **Legal Disclaimer Notice**

Vishay

#### **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and / or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.